- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360752 > ICS627R-01T Inductor; Inductor Type:Power; Inductance:101.31uH; Inductance Tolerance:+/- 20 %; Series:CTX; Package/Case:ECONO-PAC; Core Material:Iron; DC Current, Parallel Full Load:0.68A; DC Current, Series Full Load:0.34A RoHS Compliant: Yes PDF資料下載

參數(shù)資料

| 型號: | ICS627R-01T |

| 英文描述: | Inductor; Inductor Type:Power; Inductance:101.31uH; Inductance Tolerance:+/- 20 %; Series:CTX; Package/Case:ECONO-PAC; Core Material:Iron; DC Current, Parallel Full Load:0.68A; DC Current, Series Full Load:0.34A RoHS Compliant: Yes |

| 中文描述: | HDTV機頂盒時鐘源 |

| 文件頁數(shù): | 3/4頁 |

| 文件大?。?/td> | 42K |

| 代理商: | ICS627R-01T |

ICS627-01

HDTV Set-Top Clock Source

MDS 627-01 B

Integrated Circuit Systems, Inc. 525 Race Street San Jose CA95126(408) 295-9800tel www.icst.com

3

Revision 051600

PRELIMINARY INFORMATION

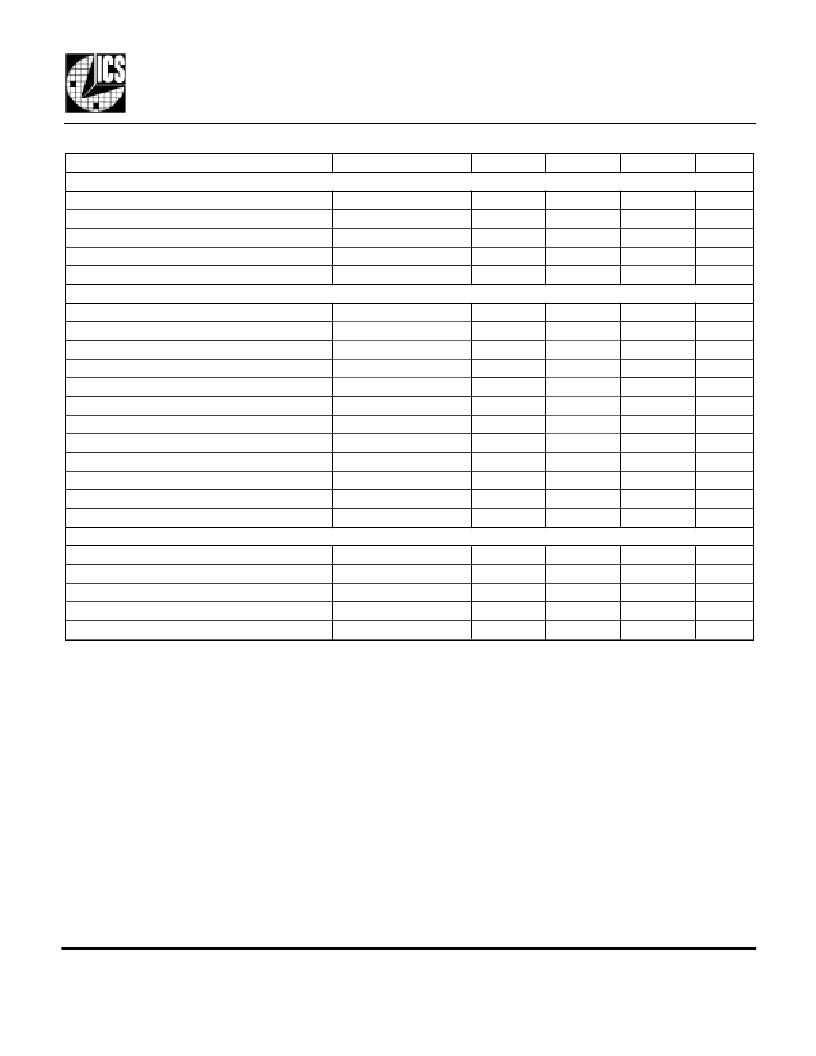

Parameter

ABSOLUTE MAXIMUM RATINGS (note 1)

Supply voltage, VDD

Inputs and Clock Outputs

Ambient Operating Temperature

Soldering Temperature

Storage temperature

DC CHARACTERISTICS (VDD = 3.3V unless noted)

Operating Voltage, VDD

Input High Voltage, VIH

Input Low Voltage, VIL

Input High Voltage, VIH, ICLK and CLKIN

Input Low Voltage, VIL, ICLK and CLKIN

Output High Voltage, VOH

Output Low Voltage, VOL

Output High Voltage, VOH, CMOS level

Operating Supply Current, IDD

Short Circuit Current

Input Capacitance

Frequency synthesis error

AC CHARACTERISTICS (VDD = 3.3V unless noted)

Input Frequency

Output Clock Rise Time

Output Clock Fall Time

Output Clock Duty Cycle

Maximum Absolute Jitter, short term

Conditions

Minimum

Typical

Maximum

Units

Referenced to GND

Referenced to GND

7

V

V

°C

°C

°C

-0.5

0

VDD+0.5

70

260

150

Max of 10 seconds

-65

3.15

2

3.30

3.45

V

V

V

V

V

V

V

V

0.8

(VDD/2)+1

VDD/2

VDD/2

(VDD/2)-1

IOH=-12mA

IOL=12mA

IOH=-8mA

No Load, note 2

Each output

2.4

0.4

VDD-0.4

TBD

±50

7

mA

mA

pF

ppm

All clocks

0

27.0

MH z

ns

ns

%

ps

0.8 to 2.0V

2.0 to 0.8V

At VDD/2

1.5

1.5

60

40

TBD

Electrical Specifications

Notes:

1. Stresses beyond those listed under Absolute Maximum Ratings could cause permanent damage to the device. Prolonged

exposure to levels above the operating limits but below the Absolute Maximums may affect device reliability.

2. With all clocks at highest MHz.

The ICS627-01 requires a minimum number of external components for proper operation. Use a low

inductance ground plane, connect all GNDs to this. Connect 0.01μF decoupling caps across pins 5 and 10, 8

and 10, and 22 and 20, as close to the ICS627-01 as possible. A series termination resistor of 33

may be

used for each clock output. The 27.000 MHz crystal must be connected as close to the chip as possible. The

crystal should be a fundamental mode, parallel resonant. Crystal capacitors should be connected from pins X1

to ground and X2 to ground. The value of these capacitors is given by the following equation, where C

L

is the

crystal load capacitance: Crystal caps (pF) = (C

L

-6) x 2. So for a crystal with 16pF load capacitance, two 20pF

caps should be used. If a clock input is used, drive it into X1 and leave X2 unconnected.

External Components

相關PDF資料 |

PDF描述 |

|---|---|

| ICS650-01B | System Peripheral Clock Source |

| ICS650R01I | System Peripheral Clock Source |

| ICS650-07B | Broadcom Clock Source |

| ICS650-07C | Networking Clock Source |

| ICS650-11B | BroadCom Networking Clock Synthesizer |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| ICS-628-AGG | 制造商:Samtec Inc 功能描述:CONN DIP SCKT SKT 28 POS 2.54MM SLDR ST TH - Bulk |

| ICS-628-AGT | 制造商:Samtec Inc 功能描述:CONN DIP SCKT SKT 28 POS 2.54MM SLDR ST TH - Bulk |

| ICS-628-ATT | 制造商:Samtec Inc 功能描述:CONN DIP SCKT SKT 28 POS 2.54MM SLDR ST TH - Bulk |

| ICS-628-EGG | 制造商:Samtec Inc 功能描述:CONN DIP SCKT SKT 28 POS 2.54MM SLDR ST TH - Bulk |

| ICS-628-EGT | 制造商:Samtec Inc 功能描述:CONN DIP SCKT SKT 28 POS 2.54MM SLDR ST TH - Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復。