- 您現(xiàn)在的位置:買賣IC網 > PDF目錄67684 > ICS1493K-17LFT (INTEGRATED CIRCUIT TECHNOLOGY CORP) 48 MHz, PROC SPECIFIC CLOCK GENERATOR, QCC20 PDF資料下載

參數資料

| 型號: | ICS1493K-17LFT |

| 廠商: | INTEGRATED CIRCUIT TECHNOLOGY CORP |

| 元件分類: | 時鐘產生/分配 |

| 英文描述: | 48 MHz, PROC SPECIFIC CLOCK GENERATOR, QCC20 |

| 封裝: | 4 X 4 MM, ROHS COMPLIANT, QFN-20 |

| 文件頁數: | 9/11頁 |

| 文件大?。?/td> | 217K |

| 代理商: | ICS1493K-17LFT |

Clock Synthesizer for Portable Systems

MDS 1493-17 A

7

Revision 101005

Integr ated Circuit System s

● 525 Ra ce Stree t, Sa n Jose, CA 951 26 ● te l (4 08) 297 -1201 ● www.icst.com

ICS1493-17

PRELIMINAR Y INFORMA T ION

Serial Data Interface

Data Protocol

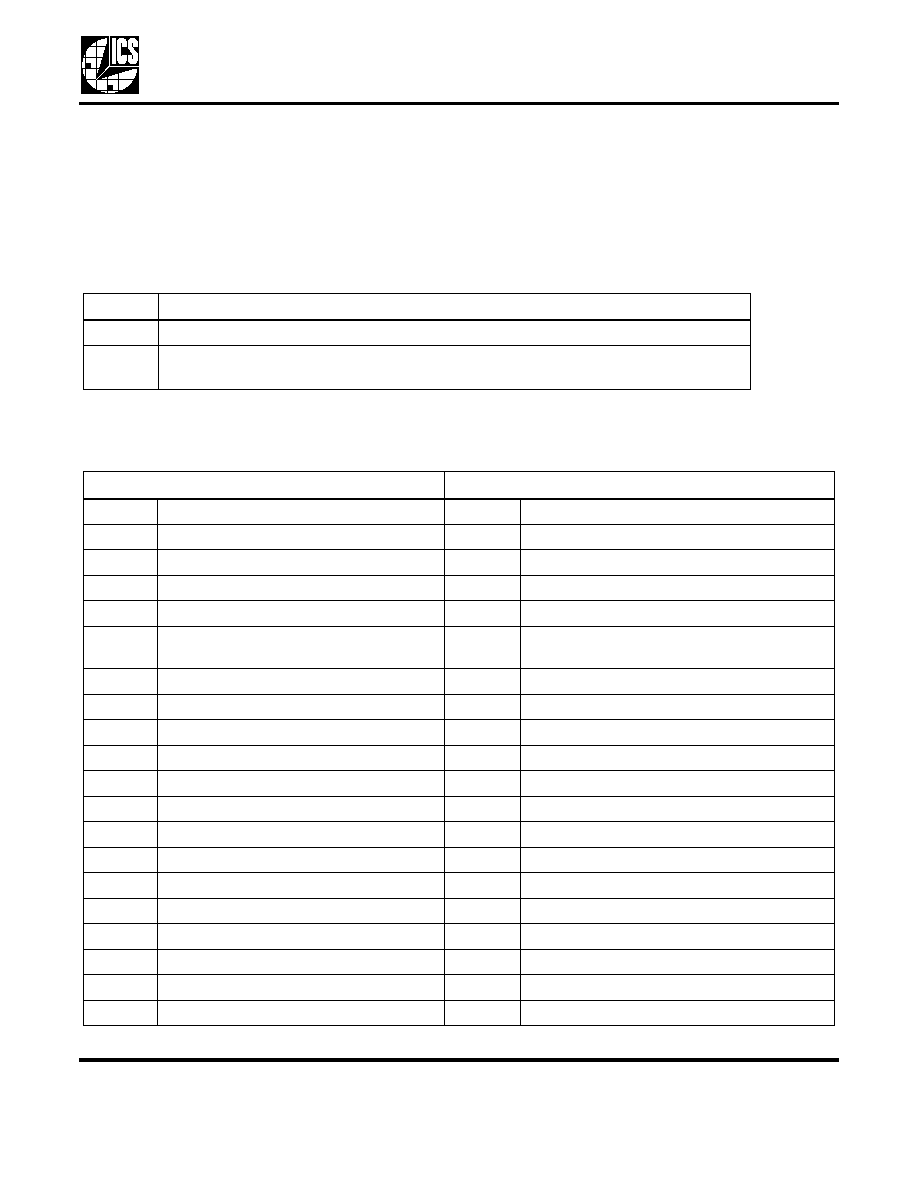

The clock driver serial protocol accepts byte write, byte read, block write, and block read operations from the

controller. For block write/read operation, the bytes must be accessed in sequential order from lowest to highest

byte (most significant bit first) with the ability to stop after any complete byte has been transferred. For byte write

and byte read operations, the system controller can access individually indexed bytes. The offset of the indexed

byte is encoded in the command code, as described in the following table.

The block write and block read protocol is outlined in the table below, followed by the corresponding byte write and

byte read protocol. The slave receiver address is 11010010 (D2h).

Bit

Description

7

0 = Block read or block write operation, 1 = Byte read or byte write operation

(6:0)

Byte offset for byte read or byte write operation. For block read or block write operations,

these bits should be '0000000'.

Block Write Protocol

Block Read Protocol

Bit

Description

Bit

Description

1

Start

1

Start

2:8

Slave address - 7 bits

2:8

Slave address - 7 bits

9

Write = 0

9

Write = 0

10

Acknowledge from slave

10

Acknowledge from slave

11:18

Command code — 8 bit

‘00000000’ stands for block operation

11:18

Command code - 8 bit

‘00000000’ stands for block operation

19

Acknowledge from slave

19

Acknowledge from slave

20:27

Byte count — 8 bits

20

Repeat start

28

Acknowledge from slave

21:27

Slave address — 7 bits

29:36

Data byte 0 — 8 bits

28

Read = 1

37

Acknowledge from slave

29

Acknowledge from slave

38:45

Data byte 1 — 8 bits

30:37

Byte count from slave — 8 bits

46

Acknowledge from slave

38

Acknowledge from master

....

.............................

39:46

Data byte from slave — 8 bits

....

Data byte (N-1) — 8 bits

47

Acknowledge from master

....

Acknowledge from slave

48:55

Data byte from slave — 8 bits

....

Data byte N — 8 bits

56

Acknowledge from master

....

Acknowledge from slave

....

Data byte N from slave — 8 bits

....

Stop

....

Not Acknowledge from master

....

Stop

相關PDF資料 |

PDF描述 |

|---|---|

| ICS1493K-17LF | 48 MHz, PROC SPECIFIC CLOCK GENERATOR, QCC20 |

| ICS1493K-17LFT | 48 MHz, PROC SPECIFIC CLOCK GENERATOR, QCC20 |

| ICS1522MLF | 230 MHz, VIDEO CLOCK GENERATOR, PDSO24 |

| ICS1524AMT | 250 MHz, OTHER CLOCK GENERATOR, PDSO24 |

| ICS1524AM | 250 MHz, OTHER CLOCK GENERATOR, PDSO24 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ICS1494M-XXX | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Peripheral IC |

| ICS1494N-XXX | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Peripheral IC |

| ICS1522 | 制造商:ICS 制造商全稱:ICS 功能描述:User-Programmable Video Clock Generator/ Line-Locked Clock Regenerator |

| ICS1522M | 制造商:ICS 制造商全稱:ICS 功能描述:User-Programmable Video Clock Generator/ Line-Locked Clock Regenerator |

| ICS1523 | 制造商:ICS 制造商全稱:ICS 功能描述:High-Performance Programmable Line-Locked Clock Generator |

發(fā)布緊急采購,3分鐘左右您將得到回復。