- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67682 > IBM25PPC750L-GB400A2T 32-BIT, 400 MHz, RISC PROCESSOR, CBGA360 PDF資料下載

參數(shù)資料

| 型號: | IBM25PPC750L-GB400A2T |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 32-BIT, 400 MHz, RISC PROCESSOR, CBGA360 |

| 封裝: | 25 X 25 MM, 1.27 MM PITCH, CERAMIC, BGA-360 |

| 文件頁數(shù): | 3/48頁 |

| 文件大?。?/td> | 608K |

| 代理商: | IBM25PPC750L-GB400A2T |

第1頁第2頁當前第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁

12/8/99

Version 1.02

Page 11

PowerPC 740 and PowerPC 750 Microprocessor

CMOS 0.20

m Copper Technology, PID-8p, PPC740L and PPC750L, dd3.2

3

Resolution

4

—

°C3

4

Drift, all sources

—

.25

LSb

5

Linearity, error over range

—

1

LSb

6

Offset error, reducible

—

2

LSb

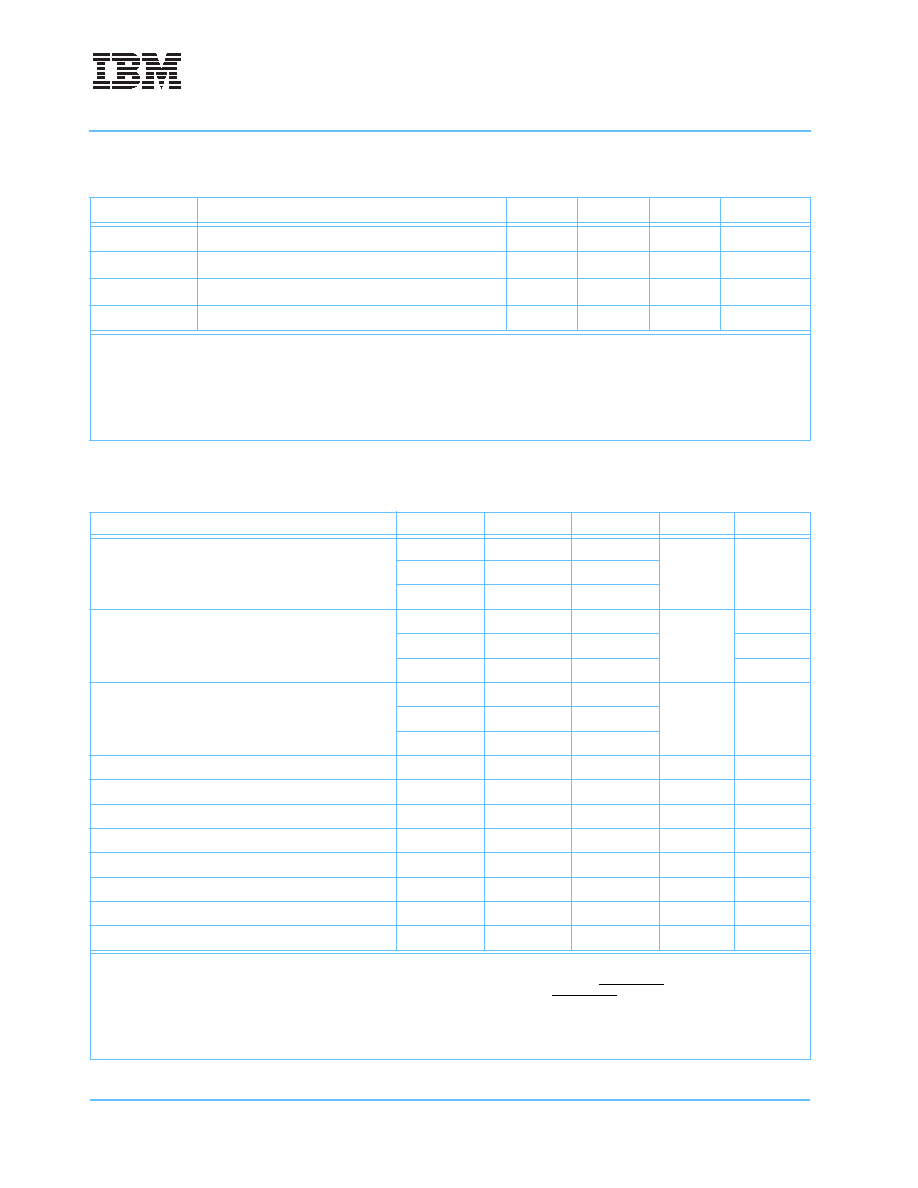

DC Electrical Specications

See Section “Recommended Operating Conditions,” on page 9, for operating conditions.

Characteristic

Symbol

Min

Max

Unit

Notes

Input high voltage (all inputs except SYSCLK)

V

IH(3.3V)

2.0

3.465

V

1,2

V

IH(2.5V)

1.75

2.625

V

IH()1.8V

1.4

1.89

Input low voltage (all inputs except SYSCLK)

V

IL(3.3V)

GND

0.8

V

IL(2.5V)

GND

0.7

V

IL()1.8V

GND

0.5

SYSCLK input high voltage

CV

IH(3.3V)

2.0

3.465

V

1, 4

CV

IH(2.5V)

2.0

2.625

CV

IH(1.8V)

1.5

1.89

SYSCLK input low voltage

CV

IL

–

0.4

V

4

Input leakage current, V

IN = OVDD

I

IN

–20

A

1,2

Hi-Z (off state) leakage current, Vin = OV

DD

I

TSI

–20

A

1,2

Output high voltage, I

OH = –6mA

V

OH(3.3V)

2.4

–

V

Output high voltage, I

OH = –6mA

V

OH((2.5V))

1.9

–

V

Output high voltage, I

OH = –3mA

V

OH(1.8V)

1.4

–

V

Output low voltage, I

OL = 6mA

V

OL

–

0.4

V

Capacitance, V

IN =0 V, f = 1MHz

C

IN

–

5.0

pF

2,3

Note:

1. For 60x bus signals, the reference is OVDD, while L2OVDD is the reference for the L2 bus signals.

2. JTAG port signal levels are controlled by the BVSEL pin and are the same as those shown for the 60x bus. LSSD_MODE, L1_TSTCLK, and L2TSTCLK

receiver voltage levels are those shown for OVdd = 1.8V nominal, regardless of BVSEL. JTAG, LSSD_MODE, L1_TSTCLK, and L2TSTCLK values in

this table are guaranteed by design and characterization, and are not tested.

3. Capacitance values are guaranteed by design and characterization, and are not tested.

4. SYSCLK input high and low voltage: I/O timings are measured using a “rail to rail” SYSCLK; I/O timing may be less favorable if SYSCLK does not travel

from GND to OVDD.

Thermal Sensor Specications

See Table “Recommended Operating Conditions,” on page 9, for operating conditions.

Num

Characteristic

Minimum

Maximum

Unit

Notes

Note:

1. The temperature is the junction temperature of the die. The thermal assist unit's (TAU) raw output does not indicate an absolute temperature, but it

must be interpreted by software to derive the absolute junction temperature. For information on how to use and calibrate the TAU, contact

ppcsupp@us.ibm.com. This specification reflects the temperature span supported by the design.

2. The comparator settling time value must be converted into the number of CPU clocks that need to be written into the THRM3 SPR. For parts with

nominal operating frequencies (speed sort) above 266 MHz, the settling time = 20

s × (266/nominal frequency). For example: for 500 MHz parts,

settling time = 20

s × (266/500) = 10.6 s. It is recommended that the maximum value be set in THRM3 under all conditions.

3. This value is guaranteed by design and is not tested.

相關PDF資料 |

PDF描述 |

|---|---|

| IBM25PPC750-DB0M2500 | 32-BIT, 250 MHz, RISC PROCESSOR, CBGA360 |

| IBM25PPC750CX-CP30-3T | 32-BIT, 433 MHz, RISC PROCESSOR, PBGA256 |

| IBM25PPC750CX-CP40-3T | 32-BIT, 466 MHz, RISC PROCESSOR, PBGA256 |

| IBM25PPC750CXEFP10-3T | RISC PROCESSOR, PBGA256 |

| IBM25PPC750CXEJP7012T | 32-BIT, 600 MHz, RISC PROCESSOR, PBGA256 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| IBM25PPC750L-GB400C2R | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| IBM25PPC750L-GB400C2SR | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| IBM25PPC750L-GB400C2ST | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| IBM25PPC750L-GB400C2T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| IBM25PPC750L-GB400D2R | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

發(fā)布緊急采購,3分鐘左右您將得到回復。