- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67682 > IBM25NPE405L-3FA266CZ 32-BIT, 266 MHz, RISC PROCESSOR, PBGA324 PDF資料下載

參數(shù)資料

| 型號(hào): | IBM25NPE405L-3FA266CZ |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 32-BIT, 266 MHz, RISC PROCESSOR, PBGA324 |

| 封裝: | 23 X 23 MM, PLASTIC, EBGA-324 |

| 文件頁數(shù): | 43/52頁 |

| 文件大小: | 907K |

| 代理商: | IBM25NPE405L-3FA266CZ |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁當(dāng)前第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

Preliminary

PowerNP NPe405L Embedded Processor Data Sheet

48

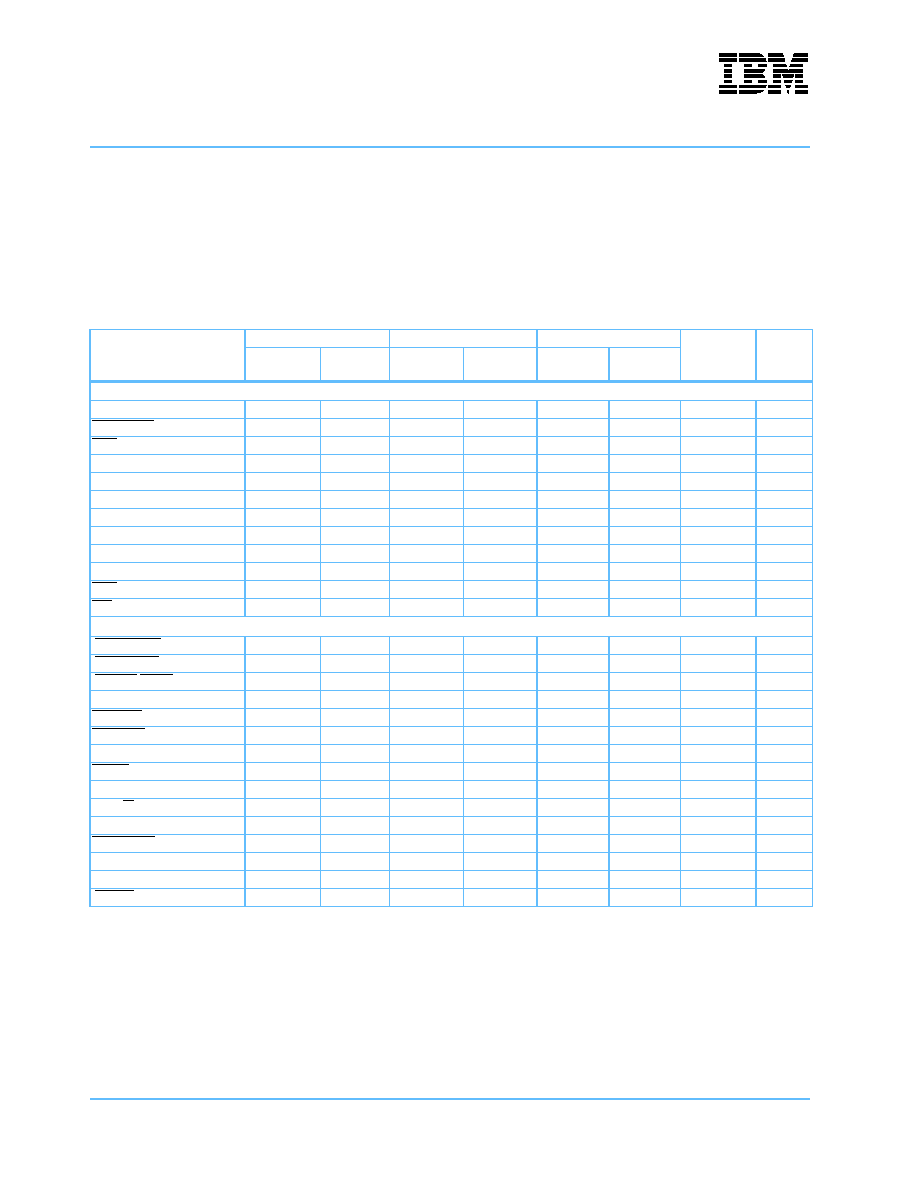

SDRAM Interface

BA1:0

n/a

7.2

1.5

19

12

SysClk

2, 3

BankSel3:0

n/a

5.8

1.0

19

12

SysClk

3

CAS

n/a

7.0

1.4

19

12

SysClk

2, 3

ClkEn0:1

n/a

4.9

1.0

40

25

SysClk

3

DQM0:3

n/a

5.9

1.0

19

12

SysClk

3

DQMCB

n/a

5.9

1.0

19

12

SysClk

3

ECC0:7

2.0

0.3

5.7

1.0

19

12

SysClk

3

MemAddr12:00

n/a

7.2

1.4

19

12

SysClk

2, 3

MemClkOut0:1

n/a

0.4

-1.2

19

12

SysClk

3, 4

MemData00:31

2.0

0.3

5.6

1.0

19

12

SysClk

3

RAS

n/a

7.4

1.6

19

12

SysClk

2, 3

WE

n/a

7.1

1.4

19

12

SysClk

2, 3

External Peripheral Bus Interface

[DMAReq0:3]

[4.8]

[0.0]

[7.0]

[1.1]

n/a

PerClk

[DMAAck0:3]

n/a

[7.5]

[1.1]

12

8

PerClk

[EOT0:3/TC0:3]

[4.3]

[-0.1]

[8.5]

[1.2]

12

8

PerClk

PerAddr04:31

n/a

8.5

0.9

17

11

PerClk

PerBLast

n/a

7.4

1.4

12

8

PerClk

PerCS0:3

n/a

7.2

1.3

12

8

PerClk

PerData00:15

4.8

1.0

9.3

1.0

17

11

PerClk

PerOE

n/a

7.6

1.4

12

8

PerClk

PerPar0:1

3.1

0.0

8.3

0.9

17

11

PerClk

PerR/W

n/a

7.5

1.4

12

8

PerClk

PerReady

7.5

-0.5

n/a

PerClk

PerWBE0:1

n/a

7.5

1.3

12

8

PerClk

n/a

0.5

-0.9

17

11

PLB Clk

5

PerErr

4.0

-0.6

n/a

PerClk

[PerWE]

n/a

[8.3]

[1.3]

12

8

I/O Specifications—133 and 200MHz (Part 2 of 2)

Notes:

1. Ethernet interface meets timing requirements as defined by IEEE 802.3 standard.

2. The SDRAM command interface is configurable through SDRAM0_TR[LDF] to provide a 2 to 4 cycle delay before the

command is used by SDRAM. Output times in table are in cycle 1.

3. SDRAM I/O timings are specified relative to a SysClk terminated in a lumped 10pF load.

4. SDRAM interface hold times are guaranteed at the NPe405L package pin. System designers must use the NPe405L

IBIS model (available from www.chips.ibm.com) to ensure their clock distribution topology minimizes loading and

reflections, and that the relative delays on clock wiring do not exceed the delays on other SDRAM signal wiring.

5. PerClk rising edge at package pin with a 10pF load trails the internal PLB clock by approximately 0.8ns.

Signal

Input (ns)

Output (ns)

Output Current (mA)

Clock

Notes

Setup Time

(TIS min)

Hold Time

TIH min)

Valid Delay

(TOV max)

Hold Time

(TOH min)

I/O H

(maximum)

I/O L

(minimum)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IBM25PPC405EP-3GB133CZ | 32-BIT, 133.33 MHz, RISC PROCESSOR, PBGA385 |

| IBM25PPC405EP-3GB133C | 32-BIT, 133.33 MHz, RISC PROCESSOR, PBGA385 |

| IBM25PPC405GP-3DD200C | RISC PROCESSOR, PBGA456 |

| IBM25PPC405GP-3BD266C | RISC PROCESSOR, PBGA456 |

| IBM25PPC405GP3EE200CZ | 32-BIT, 200 MHz, RISC PROCESSOR, PBGA413 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IBM25PPC403GAJC33C1 | 制造商:IBM 功能描述: |

| IBM25PPC405CR-3BC200C | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MICROPROCESSOR|32-BIT|CMOS|BGA|316PIN|PLASTIC |

| IBM25PPC405CR-3BC200CZ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MICROPROCESSOR|32-BIT|CMOS|BGA|316PIN|PLASTIC |

| IBM25PPC405CR-3BC266C | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MICROPROCESSOR|32-BIT|CMOS|BGA|316PIN|PLASTIC |

| IBM25PPC405CR-3BC266CZ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MICROPROCESSOR|32-BIT|CMOS|BGA|316PIN|PLASTIC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。