- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370783 > HYB25D128160TC-5 (INFINEON TECHNOLOGIES AG) MEMORY SPECTRUM PDF資料下載

參數(shù)資料

| 型號: | HYB25D128160TC-5 |

| 廠商: | INFINEON TECHNOLOGIES AG |

| 英文描述: | MEMORY SPECTRUM |

| 中文描述: | 記憶譜 |

| 文件頁數(shù): | 65/85頁 |

| 文件大小: | 3085K |

| 代理商: | HYB25D128160TC-5 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁當(dāng)前第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁

Data Sheet

65

Rev. 1.0, 2004-04

HYB25D128[400/800/160]C[C/E/T](L)

128 Mbit Double Data Rate SDRAM

Electrical Characteristics

4.3

AC Characteristics

(Notes 1-5 apply to the following Tables; Electrical Characteristics and DC Operating Conditions, AC Operating

Conditions,

I

DD

Specifications and Conditions, and Electrical Characteristics and AC Timing.)

Notes

1. All voltages referenced to

V

SS

.

2. Tests for AC timing,

I

DD

, and electrical, AC and DC characteristics, may be conducted at nominal reference/

supply voltage levels, but the related specifications and device operation are guaranteed for the full voltage

range specified.

3.

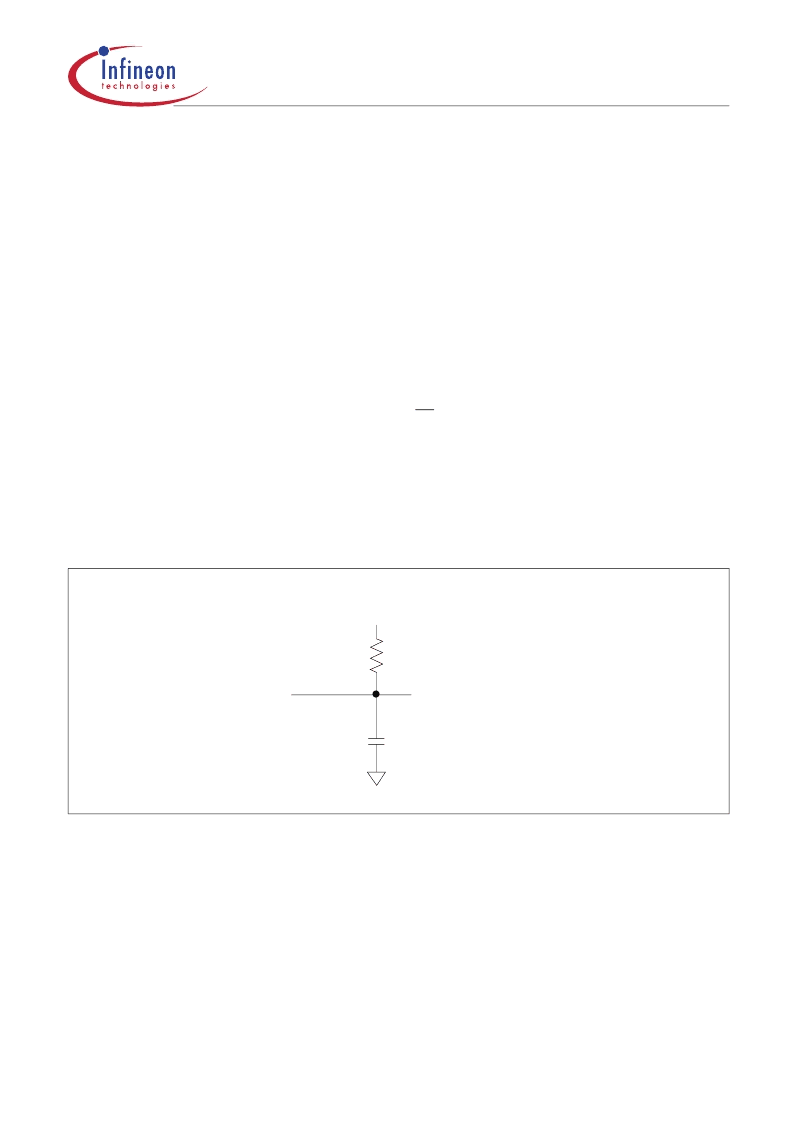

Figure 37

represents the timing reference load used in defining the relevant timing parameters of the part. It

is not intended to be either a precise representation of the typical system environment nor a depiction of the

actual load presented by a production tester. System designers will use IBIS or other simulation tools to

correlate the timing reference load to a system environment. Manufacturers will correlate to their production

test conditions (generally a coaxial transmission line terminated at the tester electronics).

4. AC timing and

I

DD

tests may use a

V

IL

to

V

IH

swing of up to 1.5 V in the test environment, but input timing is

still referenced to

V

REF

(or to the crossing point for CK, CK), and parameter specifications are guaranteed for

the specified AC input levels under normal use conditions. The minimum slew rate for the input signals is 1 V/

ns in the range between

V

IL(AC)

and

V

IH(AC)

.

5. The AC and DC input level specifications are as defined in the SSTL_2 Standard (i.e. the receiver effectively

switches as a result of the signal crossing the AC input level, and remains in that state as long as the signal

does not ring back above (below) the DC input LOW (HIGH) level).

6. For System Characteristics like Setup & Holdtime Derating for Slew Rate, I/O Delta Rise/Fall Derating, DDR

SDRAM Slew Rate Standards, Overshoot & Undershoot specification and Clamp

V

-

I

characteristics see the

latest JEDEC specification for DDR components.

Figure 37

AC Output Load Circuit Diagram / Timing Reference Load

50

Timing Reference Point

Output

(

V

OUT

)

30 pF

V

TT

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HYB25D128160TC-6 | MEMORY SPECTRUM |

| HYB25D128160TC-7 | MEMORY SPECTRUM |

| HYB25D128160TC-75 | MEMORY SPECTRUM |

| HYB25D128160TC-7F | MEMORY SPECTRUM |

| HYB25D128160TC-8 | MEMORY SPECTRUM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HYB25D128160TC-6 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:MEMORY SPECTRUM |

| HYB25D128160TC-7 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:MEMORY SPECTRUM |

| HYB25D128160TC-75 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:MEMORY SPECTRUM |

| HYB25D128160TC-7F | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:MEMORY SPECTRUM |

| HYB25D128160TC-8 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:MEMORY SPECTRUM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。