- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄370783 > HYB25D128160CT-5 (INFINEON TECHNOLOGIES AG) 128 Mbit Double Data Rate SDRAM PDF資料下載

參數(shù)資料

| 型號(hào): | HYB25D128160CT-5 |

| 廠(chǎng)商: | INFINEON TECHNOLOGIES AG |

| 英文描述: | 128 Mbit Double Data Rate SDRAM |

| 中文描述: | 128兆雙倍數(shù)據(jù)速率SDRAM |

| 文件頁(yè)數(shù): | 21/85頁(yè) |

| 文件大?。?/td> | 3085K |

| 代理商: | HYB25D128160CT-5 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)當(dāng)前第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)

Data Sheet

21

Rev. 1.0, 2004-04

HYB25D128[400/800/160]C[C/E/T](L)

128 Mbit Double Data Rate SDRAM

Functional Description

3.2

Mode Register Definition

The Mode Register is used to define the specific mode of operation of the DDR SDRAM. This definition includes

the selection of a burst length, a burst type, a CAS latency, and an operating mode. The Mode Register is

programmed via the Mode Register Set command (with BA0 = 0 and BA1 = 0) and retains the stored information

until it is programmed again or the device loses power (except for bit A8, which is self-clearing).

Mode Register bits A0-A2 specify the burst length, A3 specifies the type of burst (sequential or interleaved), A4-

A6 specify the CAS latency, and A7-A11 specify the operating mode.

The Mode Register must be loaded when all banks are idle, and the controller must wait the specified time before

initiating the subsequent operation. Violating either of these requirements results in unspecified operation.

3.2.1

Read and write accesses to the DDR SDRAM are burst oriented, with the burst length being programmable. The

burst length determines the maximum number of column locations that can be accessed for a given Read or Write

command. Burst lengths of 2, 4, or 8 locations are available for both the sequential and the interleaved burst types.

Burst Length

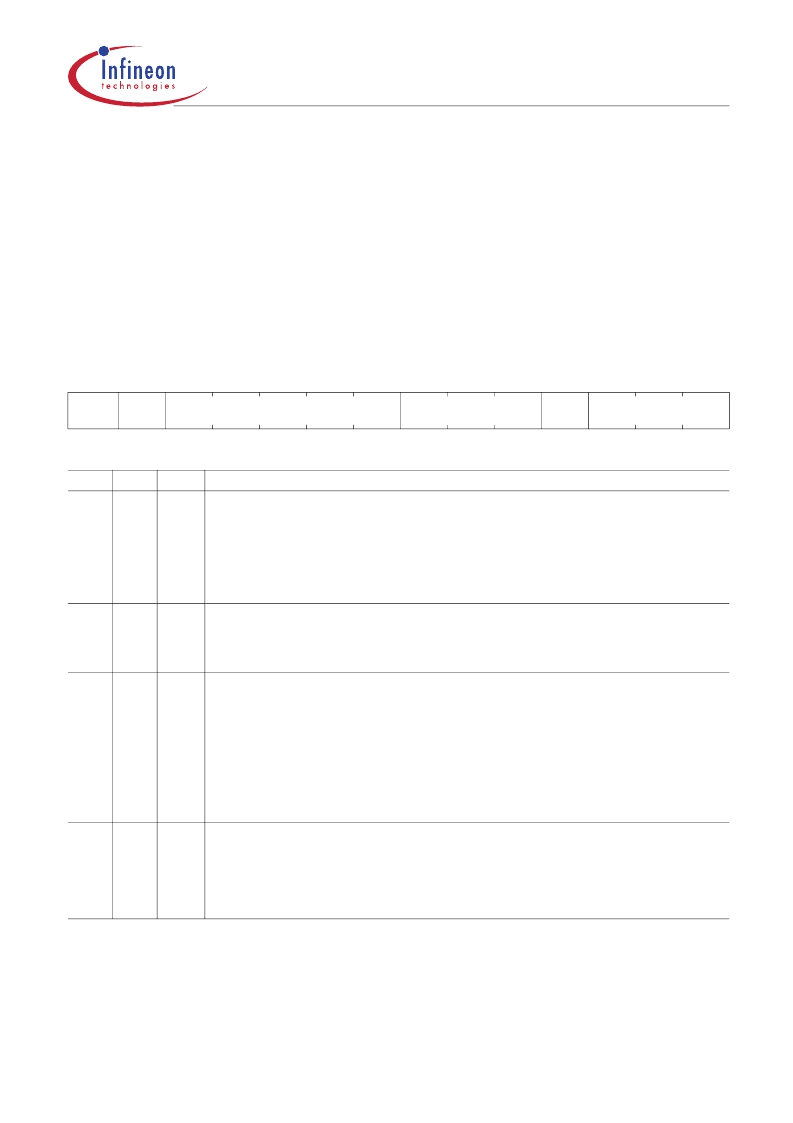

MR

Mode Register Definition

(BA[1:0] = 00

B

)

BA1

BA0

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

0

0

MODE

CL

BT

BL

reg. addr

w

w

w

w

Field

BL

Bits

[2:0]

Type

1)

w

1) w = write

Description

Burst Length

Number of sequential bits per DQ related to one read/write command; see

Chapter 3.2.1

.

Note:All other bit combinations are RESERVED.

001 2

010 4

011 8

Burst Type

See

Table 5

for internal address sequence of low order address bits; see

Chapter 3.2.2

.

0

Sequential

1

Interleaved

CAS Latency

Number of full clocks from read command to first data valid window; see

Chapter 3.2.3

.

Note:All other bit combinations are RESERVED.

BT

3

w

CL

[6:4]

w

010 2

011 3

101 1.5

Note:DDR200 components only

110 2.5

Operating Mode

See

Chapter 3.2.4

.

Note:All other bit combinations are RESERVED.

MODE

[12:7] w

000000

000010

Normal Operation without DLL Reset

Normal Operation with DLL Reset

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HYB25D128160CT-6 | 128 Mbit Double Data Rate SDRAM |

| HYB25D128160TC-3 | MEMORY SPECTRUM |

| HYB25D128160TC-37 | MEMORY SPECTRUM |

| HYB25D128160TC-5 | MEMORY SPECTRUM |

| HYB25D128160TC-6 | MEMORY SPECTRUM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HYB25D128160CT-6 | 制造商:Infineon Technologies AG 功能描述:8M X 16 DDR DRAM, 0.7 ns, PDSO66 |

| HYB25D128160TC-3 | 制造商:INFINEON 制造商全稱(chēng):Infineon Technologies AG 功能描述:MEMORY SPECTRUM |

| HYB25D128160TC-37 | 制造商:INFINEON 制造商全稱(chēng):Infineon Technologies AG 功能描述:MEMORY SPECTRUM |

| HYB25D128160TC-5 | 制造商:INFINEON 制造商全稱(chēng):Infineon Technologies AG 功能描述:MEMORY SPECTRUM |

| HYB25D128160TC-6 | 制造商:INFINEON 制造商全稱(chēng):Infineon Technologies AG 功能描述:MEMORY SPECTRUM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。