- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄11020 > HSP43216VC-52Z (Intersil)IC HALFBAND FILTER 100-MQFP PDF資料下載

參數(shù)資料

| 型號(hào): | HSP43216VC-52Z |

| 廠商: | Intersil |

| 文件頁(yè)數(shù): | 19/20頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | IC HALFBAND FILTER 100-MQFP |

| 標(biāo)準(zhǔn)包裝: | 66 |

| 濾波器類型: | 半帶 |

| 濾波器數(shù): | 4 |

| 電源電壓: | 4.75 V ~ 5.25 V |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 100-BQFP |

| 供應(yīng)商設(shè)備封裝: | 100-MQFP(14x20) |

| 包裝: | 托盤 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)當(dāng)前第19頁(yè)第20頁(yè)

8

FN3365.10

October 6, 2008

Operational Modes

Decimate By 2 Filter Mode (Mode1-0 = 00)

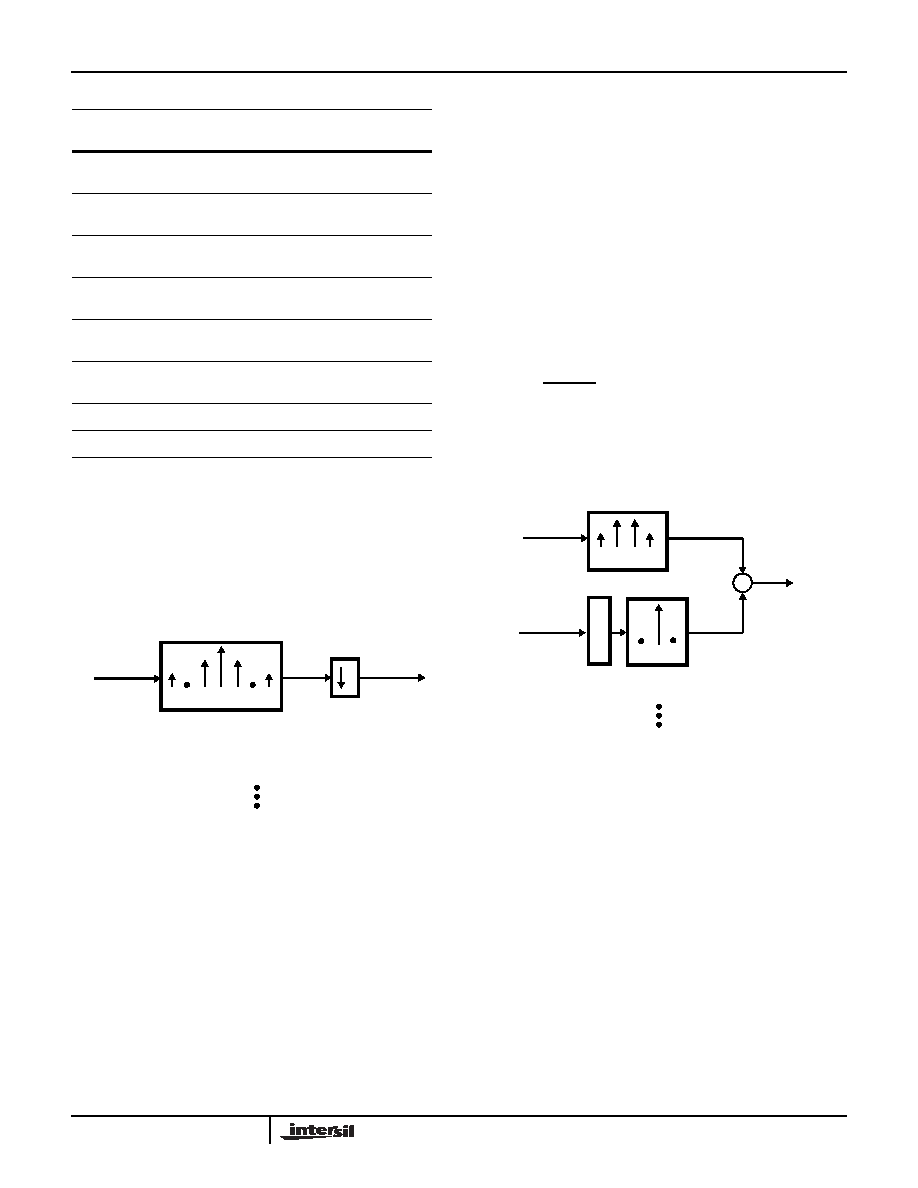

The concept of operation for Decimate by Two Filter mode is

most easily understood by comparing the 7 tap transversal

filter implementation to the equivalent polyphase

implementation. The transversal implementation is shown in

Figure 5.

By inspecting the sum-of-products for the decimated output

in Figure 5, it is seen that even indexed input samples are

always multiplied by the even filter coefficients and the odd

samples are always multiplied by the odd coefficients. This

computational partitioning is realized in the polyphase

implementation shown in Figure 6.

In the polyphase implementation, the input data is broken into

even and odd sample streams which are processed by a set

of polyphase filters running at one half of the input data rate.

These filters are designated as even or odd tap filters

depending upon whether the coefficients were derived from

the even or odd indexed coefficients of the original transversal

filter. This architecture only produces the outputs which are

not discarded by the decimation process. NOTE: Since the

only non-zero tap for a halfband filter is the center tap,

the Odd Tap Filter reduces to a delay and multiply

operation.

The operation of the HSP43216 in Decimate by Two mode is

analogous to the polyphase implementation in Figure 6. In

this mode, the internal data paths are routed as shown in

Figure 7A and Figure 7B. The different data flows depend on

whether internal or external multiplexing has been selected

using the INT/EXT control input. In either case, an input data

stream is decomposed into even and odd sample streams

which are then routed to the even and odd tap polyphase

filters. The output of each polyphase filter is summed and

output via AOUT0-15.

TABLE 5. OUTPUT ROUNDING CONTROL

RND

2-0

ROUND FUNCTION

000

Round output to 8-bits, AOUT15-8 and BOUT15-8, zero

lower bits.

001

Round output to 9-bits, AOUT15-7 and BOUT15-7, zero

lower bits.

010

Round output to 10-bits, AOUT15-6 and BOUT15-6,

zero lower bits.

011

Round output to 11-bits, AOUT15-5 and BOUT15-5,

zero lower bits.

100

Round output to 12-bits, AOUT15-4 and BOUT15-4,

zero lower bits.

101

Round output to 14-bits, AOUT15-2 and BOUT15-2,

zero lower bits.

110

Round output to 16-bits, AOUT15-0 and BOUT15-0.

111

Zero all outputs.

C0 C1 C2 C3 C4 C5 C6

X3,X2,X1,X0

Y(0) = X0(C0)+X1(C1)+X2(C2)+X3(C3)+X4(C4)+X5(C5)+X6(C6)

Y(1) = X1(C0)+X2(C1)+X3(C2)+X4(C3)+X5(C4)+X6(C5)+X7(C6)

Y(2) = X2(C0)+X3(C1)+X4(C2)+X5(C3)+X6(C4)+X7(C5)+X8(C6)

Y(3) = X3(C0)+X4(C1)+X5(C2)+X6(C3)+X7(C4)+X8(C5)+X9(C6)

...,Y1,Y0

2

..,Y4,Y2,Y0

Indicates samples discarded by decimation process

FIGURE 5. TRANSVERSAL IMPLEMENTATION OF

DECIMATE BY 2 HALFBAND FILTER

C0 C2 C4 C6

...,X4,X2,X0

Y(0) = X0(C0)+X1(C1)+X2(C2)+X3(C3)+X4(C4)+X5(C5)+X6(C6)

Y(1) = X2(C0)+X3(C1)+X4(C2)+X5(C3)+X6(C4)+X7(C5)+X8(C6)

..,Y2,Y1,Y0

C1 C3 C5

R

E

G

ODD TAP FILTER

EVEN TAP FILTER

...,X5,X3,X1

+

FIGURE 6. POLYPHASE IMPLEMENTATION OF DECIMATE

BY 2 HALFBAND FILTER

HSP43216

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC9S08RE8FJE | IC MCU 8K FLASH 8MHZ 32-LQFP |

| LTC1061ACN | IC FILTER BUILDNG BLK TRPL 20DIP |

| S9S08SG4E2CTG | IC MCU 8BIT 4KB FLASH 16TSSOP |

| S9S08SG4E2CSC | MCU 4K FLASH 8-SOIC |

| MC9S08SH8CFK | MCU 8BIT 8K FLASH 24-QFN |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HSP43220 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Decimating Digital Filter |

| HSP43220/883 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Decimating Digital Filter |

| HSP43220_04 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Decimating Digital Filter |

| HSP43220883 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Decimating Digital Filter |

| HSP43220GC-15 | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Harris Corporation 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。