- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371881 > HPC46004VF20 (National Semiconductor Corporation) High-Performance microController with A/D PDF資料下載

參數(shù)資料

| 型號: | HPC46004VF20 |

| 廠商: | National Semiconductor Corporation |

| 英文描述: | High-Performance microController with A/D |

| 中文描述: | 高性能微控制器/數(shù) |

| 文件頁數(shù): | 22/39頁 |

| 文件大小: | 430K |

| 代理商: | HPC46004VF20 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁當(dāng)前第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁

Timer Overview

(Continued)

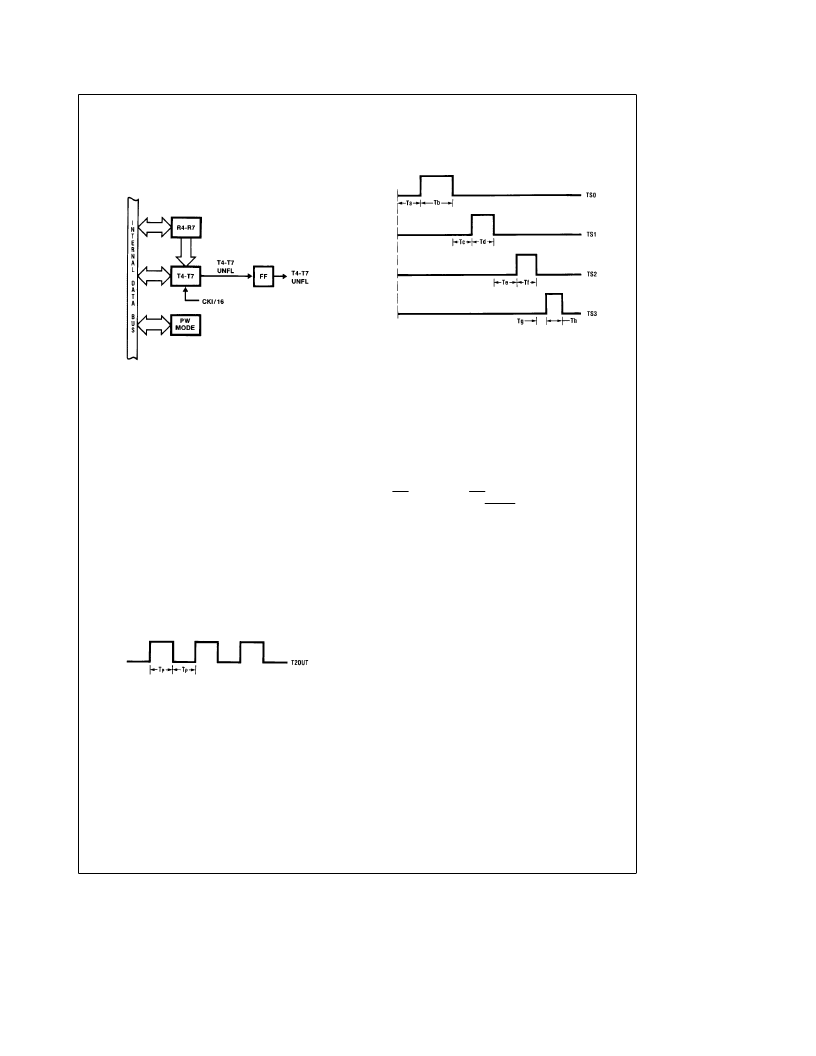

Timer/register pairs 4–7 form four identical units which can

generate synchronous outputs on port P (see Figure 21).

Maximum output frequency for any timer output can be ob-

tained by setting timer/register pair to zero. This then will

produce an output frequency equal to

(/2

the frequency of

the source used for clocking the timer.

TL/DD/9682–23

FIGURE 21. Timers T4–T7 Block

Timer Registers

There are four control registers that program the timers. The

divide by (DIVBY) register programs the clock input to tim-

ers T2 and T3. The timer mode register (TMMODE) contains

control bits to start and stop timers T1 through T3. It also

contains bits to latch, acknowledge and enable interrupts

from timers T0 through T3. The control register PWMODE

similarly programs the pulse width timers T4 through T7 by

allowing them to be started, stopped, and to latch and en-

able interrupts on underflows. The PORTP register contains

bits to preset the outputs and enable the synchronous timer

output functions.

Timer Applications

The use of Pulse Width Timers for the generation of various

waveforms is easily accomplished by the HPC46164.

Frequencies can be generated by using the timer/register

pairs. A square wave is generated when the register value is

a constant. The duty cycle can be controlled simply by

changing the register value.

TL/DD/9682–24

FIGURE 22. Square Wave Frequency Generation

Synchronous outputs based on Timer T2 can be generated

on the 4 outputs TS0–TS3. Each output can be individually

programmed to toggle on T2 underflow. Register R2 con-

tains the time delay between events. Figure 23 is an exam-

ple of synchronous pulse train generation.

TL/DD/9682–25

FIGURE 23. Synchronous Pulse Generation

WATCHDOG Logic

The WATCHDOG Logic monitors the operations taking

place and signals upon the occurrence of any illegal activity.

The illegal conditions that trigger the WATCHDOG logic are

potentially infinite loops and illegal addresses. Should the

WATCHDOG register not be written to before Timer T0

overflows twice, or more often than once every 4096

counts, an infinite loop condition is assumed to have oc-

curred. An illegal condition also occurs when the processor

generates an illegal address when in the Single-Chip

modes.

*

Any illegal condition forces the WATCHDOG Out-

put (WO) pin low. The WO pin is an open drain output and

can be connected to the RESET or NMI inputs or to the

users external logic.

*

Note: See Operating Modes for details.

MICROWIRE/PLUS

MICROWIRE/PLUS is used for synchronous serial data

communications (see Figure 24 ). MICROWIRE/PLUS has

an 8-bit parallel-loaded, serial shift register using SI as the

input and SO as the output. SK is the clock for the serial

shift register (SIO). The SK clock signal can be provided by

an internal or external source. The internal clock rate is pro-

grammable by the DIVBY register. A DONE flag indicates

when the data shift is completed.

The MICROWIRE/PLUS capability enables it to interface

with any of National Semiconductor’s MICROWIRE periph-

erals (i.e., A/D converters, display drivers, EEPROMs).

22

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HPC36104 | High-Performance microController with A/D |

| HPC36164 | High-Performance microController with A/D |

| HPC-DEV-ISE-E | High-Performance microController with A/D |

| HPC-DEV-ISE4 | High-Performance microController with A/D |

| HPC46004 | High-Performance microController |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HPC46004VF30 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:High-Performance microController with A/D |

| HPC46030/E17 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:16-Bit Microcontroller |

| HPC46030/V17 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:16-Bit Microcontroller |

| HPC46040RE17 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:16-Bit Microcontroller |

| HPC46040RV17 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:16-Bit Microcontroller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。