- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄296194 > HPC36400EV2 (National Semiconductor Corporation) High-Performance Communications MicroController PDF資料下載

參數(shù)資料

| 型號: | HPC36400EV2 |

| 廠商: | National Semiconductor Corporation |

| 英文描述: | High-Performance Communications MicroController |

| 中文描述: | 高性能通信微控制器 |

| 文件頁數(shù): | 5/30頁 |

| 文件大?。?/td> | 362K |

| 代理商: | HPC36400EV2 |

第1頁第2頁第3頁第4頁當(dāng)前第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁

HPC46400E Interrupts

Complex interrupt handling is easily accomplished by the

HPC46400E’s vectored interrupt scheme There are eight

possible interrupt sources as shown in Table I

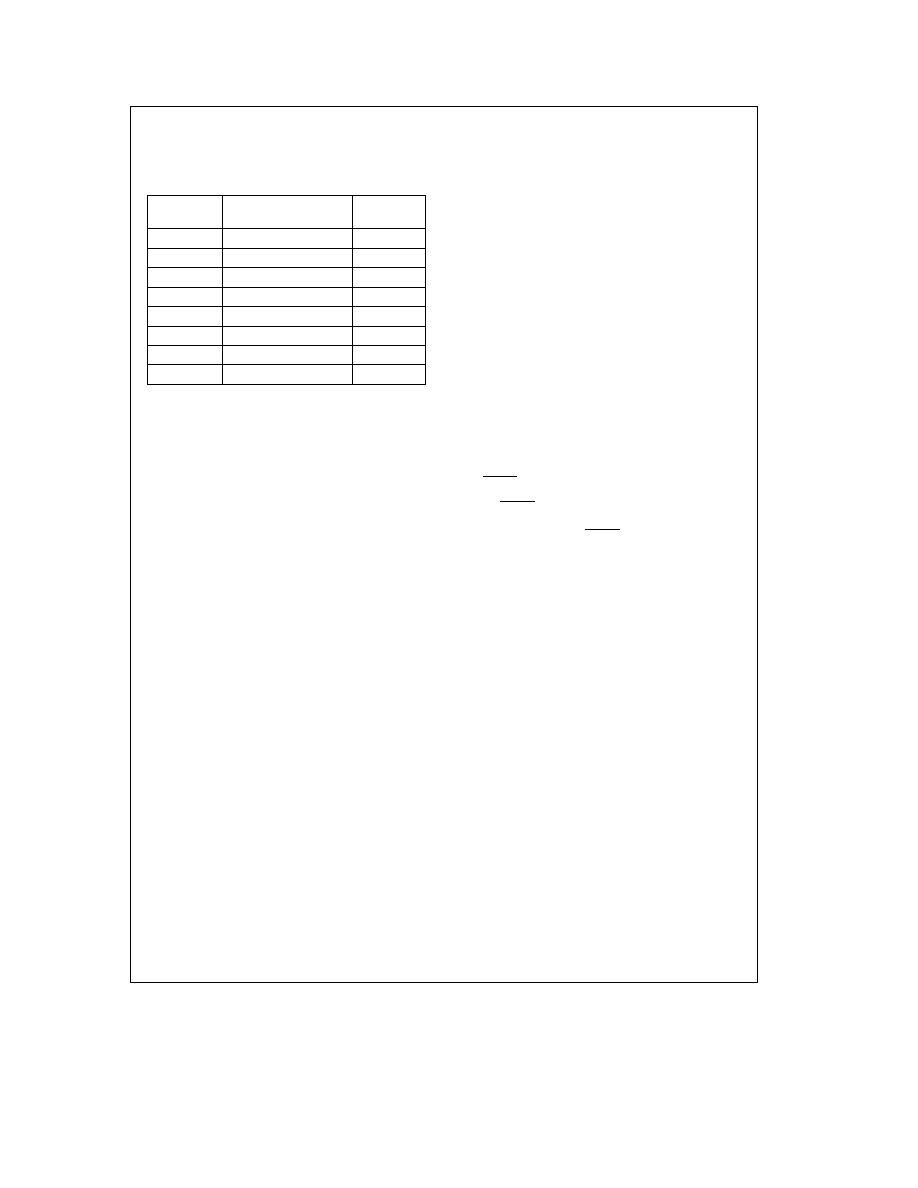

TABLE I Interrupts

Vector

Interrupt Source

Arbitration

Address

Ranking

FFFF

lFFFE

Reset

0

FFFD

lFFFC

Nonmaskable Ext (NMI)

1

FFFB

lFFFA

External on I2

2

FFF9

lFFF8

External on I3

3

FFF7

lFFF6

External on I4

4

FFF5

lFFF4

Internal on Timers

5

FFF3

lFFF2

Internal on UART

6

FFF1

lFFF0

End of Message (EOM)

7

The HPC46400E contains arbitration logic to determine

which interrupt will be serviced first if two or more interrupts

occur simultaneously Interrupts are serviced after the cur-

rent instruction is completed except for the RESET which is

serviced immediately

The NMI interrupt will immediately stop DMA activity Byte

transfers in progress will finish thereby allowing an orderly

transition to the interrupt service vector (see DMA descrip-

tion) The HDLC channels continue to operate and the user

must service data errors that might have occurred during

the NMI service routine

Interrupt Processing

Interrupts are serviced after the current instruction is com-

pleted except for the RESET which is serviced immediately

RESET holds on-chip logic in a reset state while low and

triggers the RESET interrupt on its rising edge All other

interrupts are edge-sensitive NMI is positive-edge sensitive

The external interrupts on I2 I3 and I4 can be software

selected to be rising or falling edge sensitive

Interrupt Control Registers

The HPC46400E allows the various interrupt sources and

conditions to be programmed This is done through the vari-

ous control registers A brief description of the different con-

trol registers is given below

INTERRUPT ENABLE REGISTER (ENIR)

RESET and the External Interrupt on I1 are non-maskable

interrupts The other interrupts can be individually enabled

or disabled Additionally a Global Interrupt Enable Bit in the

ENIR Register allows the Maskable interrupts to be collec-

tively enabled or disabled Thus in order for a particular

interrupt to request service both the individual enable bit

and the Global Interrupt bit (GIE) have to be set

INTERRUPT PENDING REGISTER (IRPD)

The IRPD register contains a bit allocated for each interrupt

vector The occurrence of specified interrupt trigger condi-

tions causes the appropriate bit to be set There is no indi-

cation of the order in which the interrupts have been re-

ceived The bits are set independently of the fact that the

interrupts may be disabled IRPD is a ReadWrite register

The bits corresponding to the external interrupts are normal-

ly cleared by the HPC46400E upon entering the interrupt

servicing routine

For the interrupts from the on-board peripherals the user

has the responsibility of acknowledging the interrupt

through software

INTERRUPT CONDITION REGISTER (IRCD)

Three bits of the register select the input polarity of the

external interrupt on I2 I3 and I4

Servicing the Interrupts

The Interrupt once acknowledged pushes the program

counter (PC) onto the stack thus incrementing the stack

pointer (SP) twice The Global Interrupt Enable (GIE) bit is

reset thus disabling further interrupts The program counter

is loaded with the contents of the memory at the vector

address and the processor resumes operation at this point

At the end of the interrupt service routine the user does a

RETI instruction to pop the stack set the GIE bit and return

to the main program The GIE bit can be set in the interrupt

service routine to nest interrupts if desired

Figure 10 shows

the Interrupt Enable Logic

Reset

The RESET input initializes the processor and sets all pins

at TRI-STATE except CK0 CK2 and WO HBE and ST2

have pull-downs designed to withstand override RESET is

an active-low Schmitt trigger input The processor vectors to

FFFFFFFE and resumes operation at the address con-

tained at that memory location

The RESET pin must be asserted low for at least 16 cycles

of the CK2 clock In applications using the WATCHDOG

feature RESET should be asserted for at least 64 cycles of

the CK2 clock

On application of power RESET must be held low for at

least five times the power supply rise time to ensure that the

on-chip oscillator circuit has time to stabilize

Timer Overview

The HPC46400E contains a powerful set of flexible timers

enabling the HPC46400E to perform extensive timer func-

tions not usually associated with microcontrollers

The HPC46400E contains four 16-bit timers Three of the

timers have an associated 16-bit register Timer T0 is a free-

running timer counting up at a fixed CKI16 (Clock Input

16) rate It is used for WATCHDOG logic high speed event

capture and to exit from the IDLE mode Consequently it

cannot be stopped or written to under software control Tim-

er T0 permits precise measurements by means of the cap-

ture registers I2CR I3CR and I4CR A control bit in the

register T0CON configures timer T1 and its associated reg-

ister R1 as capture registers I3CR and I2CR The capture

registers I2CR I3CR and I4CR respectively record the val-

ue of timer T0 when specific events occur on the interrupt

pins I2 I3 and I4 The control register IRCD programs the

capture registers to trigger on either a rising edge or a falling

edge of its respective input The specified edge can also be

programmed to generate an interrupt (see

Figure 11 )

The timers T2 and T3 have selectable clock rates The

clock input to these two timers may be selected from the

following two sources an external pin or derived internally

by dividing the clock input Timer T2 has additional capabili-

ty of being clocked by the timer T3 underflow This allows

the user to cascade timers T3 and T2 into a 32-bit timer

counter The control register DIVBY programs the clock in-

put to timers T2 and T3 (see

Figure 12 )

13

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HPC46003 | High-Performance microControllers |

| HPC46083 | High-Performance microControllers |

| HPC46100VF40 | HPC46100 High-Performance microController with DSP Capability |

| HPC46100 | HPC46100 High-Performance microController with DSP Capability |

| HPC46400EV2 | High-Performance Communications MicroController |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HPC36400EV20 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:High-Performance Communications MicroController |

| HPC36400EVHG2 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:High-Performance Communications MicroController |

| HPC36400EVHG20 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:High-Performance Communications MicroController |

| HPC36400L20 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:16-Bit Microcontroller |

| HPC36400T20 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:16-Bit Microcontroller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。