- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370661 > HPC3130APBKLOW-PROFILEQUA (Texas Instruments, Inc.) DIODE ZENER DUAL COMMON-CATHODE 300mW 33Vz 5mA-Izt 0.0606 0.1uA-Ir 25 SOT-23 3K/REEL PDF資料下載

參數(shù)資料

| 型號(hào): | HPC3130APBKLOW-PROFILEQUA |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | DIODE ZENER DUAL COMMON-CATHODE 300mW 33Vz 5mA-Izt 0.0606 0.1uA-Ir 25 SOT-23 3K/REEL |

| 中文描述: | 的PCI熱插拔控制器 |

| 文件頁數(shù): | 18/41頁 |

| 文件大小: | 537K |

| 代理商: | HPC3130APBKLOW-PROFILEQUA |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁當(dāng)前第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁

HPC3130A

PCI HOT PLUG CONTROLLER

SCPS055 – NOVEMBER 1999

18

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

master responds with an acknowledge signal, indicating that it requires additional data, the HPC3130A

continues to output data for each received acknowledge signal. The master terminates the sequential read

operation by not responding with an acknowledge signal, and issues a STOP condition.

b7

S b6

b4

b5

b3 b2 b1 b0 0

b7 b6 b5 b4 b3 b2 b1 b0

A

A

Slave Address

Word Address

R/W

S/P = Start/stop condition

A = Slave acknowledgment

b6

b4

b5

b3 b2 b1 b0 1

A

Data Byte

M = Master acknowledgment

S

b6

b4

b5

b3 b2 b1 b0 M

P

Slave Address

R/W

Restart

Stop

Start

Figure 5. Serial Bus Protocol – Byte Read

parallel interface

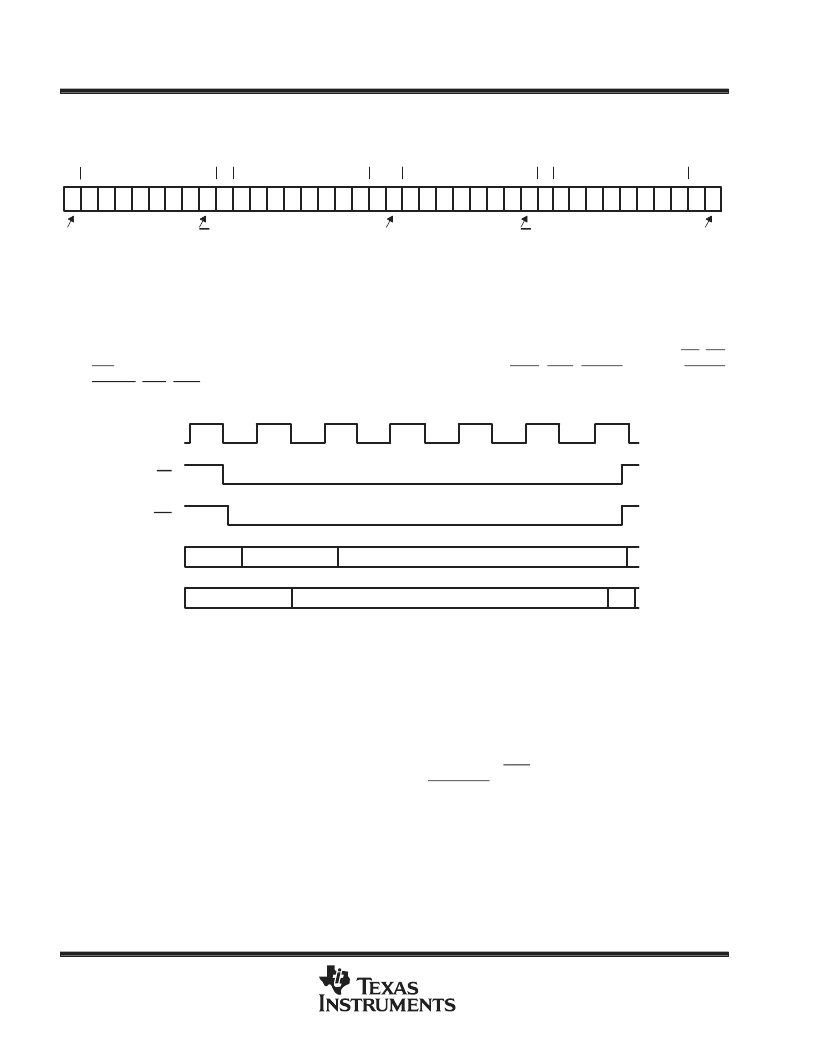

The HPC3130A also implements an 8-bit parallel interface mode. When this mode is selected, the HPC3130A

internal register addressed by the A[4:0] inputs can be accessed for a read/write transaction using the CS, RD,

WR strobes. The following signals have pullups on the mother board: IO16, M16, NOWS, CHRDY, MEMR,

MEMW, IOR, IOW, SD[15:0] to implement default states. Figure 6 shows write access using the default 8-bit

standard ISA bus cycle with four wait states. A read cycle is similar.

BCLK

CS

WR

A(0–4)

D(0–7)

Figure 6. Parallel Bus Write Cycle

connection sequencing

Before an add-in card is hot plugged and made available to the slot, the various pins in the HPC3130A have

to be controlled in a specific sequence. The HPC3130A provides the software interface to sequence the power

to the slot, clocks, and signals to the add-in cards that are being live inserted. The switch-timing block is used

to control the exact timing when the CBT switches are enabled.

The initial software sequencing is done by setting individual bits in the hot plug control register in the following

sequence. First, the SLTPWR_CTL bit is set high to drive the PWRON/OFF signal high. After the power to the

slot is applied, the SLOTRST_O bit is set low to drive the SLOTRST output. Next the CLKON_O bit is set low

to enable the PCI clock to the slot. Also, the REQ64_O bit is set to a value of 0 and the SLOTREQ64 bit is set

to indicate to the add-in card whether it is inserted into a 64-bit or 32-bit slot. SLOTREQ64 is set low for a 64-bit

slot and is set high for a 32-bit slot.

After initial software sequencing of the above signals is complete, the next step is to enable the CBT switches.

This can be done either by using the software to manually set the BUS_CTL bit or using the HPC3130A via the

automatic connection sequence mode located in the general configuration register.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HPC3130PGELOW-PROFILEQUAD | PCI HOT PLUG CONTROLLER |

| HPC3130PBMQUADFLAT | PCI HOT PLUG CONTROLLER |

| HPC3130PBKLOW-PROFILEQUAD | PCI HOT PLUG CONTROLLER |

| HPC43100VHG30 | 16-Bit Microcontroller |

| HPC46003E20 | 16-Bit Microcontroller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HPC3130APBM | 功能描述:外圍驅(qū)動(dòng)器與原件 - PCI HOT PLUG CONTROLLER RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| HPC3130APBMQUADFLAT | 制造商:TI 制造商全稱:Texas Instruments 功能描述:PCI HOT PLUG CONTROLLER |

| HPC3130APGE | 功能描述:外圍驅(qū)動(dòng)器與原件 - PCI HOT PLUG CONTROLLER RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| HPC3130APGEG4 | 功能描述:外圍驅(qū)動(dòng)器與原件 - PCI HOT PLUG CONTROLLER RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| HPC3130APGELOW-PROFILEQUA | 制造商:TI 制造商全稱:Texas Instruments 功能描述:PCI HOT PLUG CONTROLLER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。