- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄370661 > HPC3130APBKLOW-PROFILEQUA (Texas Instruments, Inc.) DIODE ZENER DUAL COMMON-CATHODE 300mW 33Vz 5mA-Izt 0.0606 0.1uA-Ir 25 SOT-23 3K/REEL PDF資料下載

參數(shù)資料

| 型號(hào): | HPC3130APBKLOW-PROFILEQUA |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | DIODE ZENER DUAL COMMON-CATHODE 300mW 33Vz 5mA-Izt 0.0606 0.1uA-Ir 25 SOT-23 3K/REEL |

| 中文描述: | 的PCI熱插拔控制器 |

| 文件頁(yè)數(shù): | 17/41頁(yè) |

| 文件大?。?/td> | 537K |

| 代理商: | HPC3130APBKLOW-PROFILEQUA |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)當(dāng)前第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)

HPC3130A

PCI HOT PLUG CONTROLLER

SCPS055 – NOVEMBER 1999

17

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

SDA

SCL

Start Condition

Stop Condition

Change of

Data Allowed

Data Line Stable, Data Valid

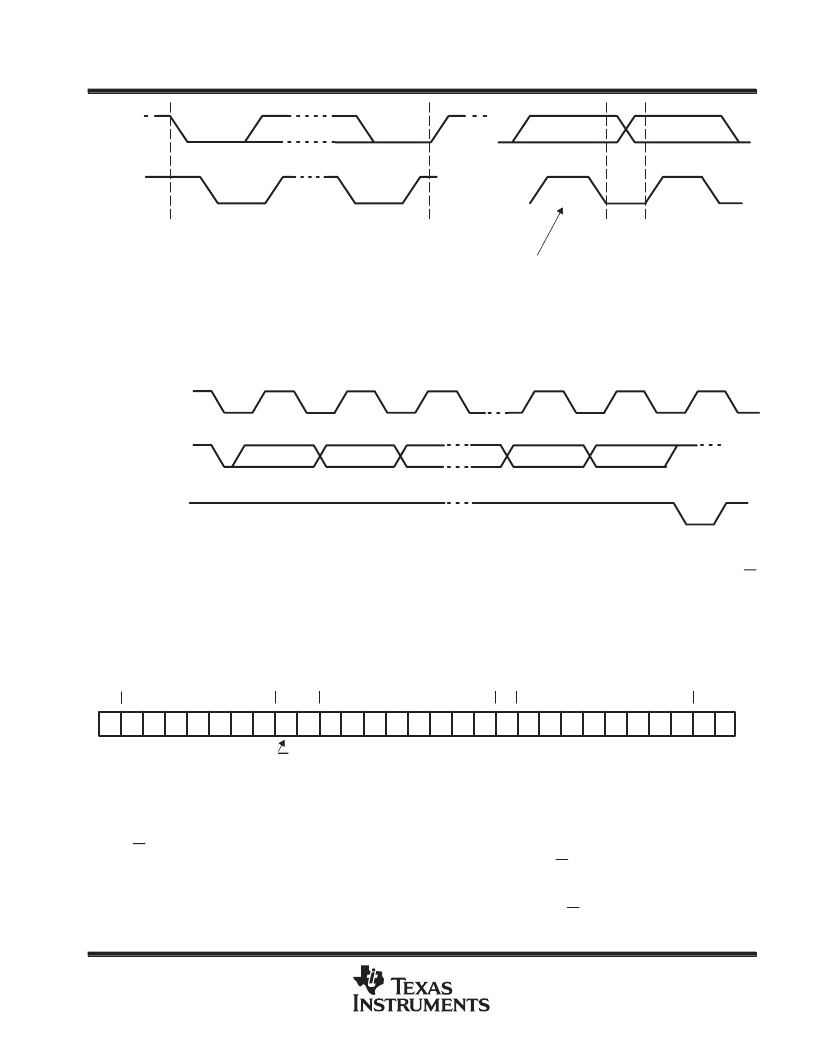

Figure 2. Serial Bus Start/Stop Conditions and Bit Transfers

Data is transferred on the bus in 8-bit bytes. The number of bytes that can be transmitted during a data transfer

is unlimited; however, each byte must be completed with an acknowledge bit. An acknowledge (ACK) is

indicated by the receiver pulling down the SDA signal so that it remains low during the high state of the SCL

signal as shown in Figure 3.

SCL From

Master

1

2

3

7

8

9

SDA Output

By Transmitter

SDA Output

By Receiver

Figure 3. Serial Bus Protocol – Acknowledge

The HPC3130A serial bus slave interface protocol for write transactions is illustrated in Figure 4. The R/W

command bit is set to zero to indicate a write transaction. For a write operation, the HPC3130A requires a word

address field after the slave address. This address field is comprised of eight bits. Upon receipt of the word

address, the HPC3130A responds with an acknowledge, and waits for the next eight bits of data, again

responding with an acknowledge. After all the data bytes are transferred, the master then terminates the transfer

by generating a STOP condition. The device automatically increments the address for subsequent data words.

After the receipt of each word, the low order address bits are internally incremented by one.

S

b6

b4

b5

b3 b2

b1 b0

0

b7 b6 b5 b4 b3

b2 b1

b0

A

A

Slave Address

Word Address

R/W

S/P = Start/stop condition

A = Slave acknowledgment

b7 b6

b4

b5

b3

b2 b1 b0

A

P

Data Byte

Figure 4. Serial Bus Protocol – Byte Write

A byte read operation is illustrated in Figure 5. The read protocol is very similar to the write protocol, except the

R/W command bit must be set to one to indicate a read data transfer. First the master issues a write command

that includes the START condition and the slave address field (with the R/W bit set to write), followed by the

address of the word it is to read. This procedure sets the internal address counter of the HPC3130A to the

desired address. After the word address acknowledgment is received by the master, the master immediately

reissues a START condition followed by another slave address field with the R/W bit set to read. The HPC3130A

responds with an acknowledgment and transmits the eight data bits stored in the addressed location. If the

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HPC3130PGELOW-PROFILEQUAD | PCI HOT PLUG CONTROLLER |

| HPC3130PBMQUADFLAT | PCI HOT PLUG CONTROLLER |

| HPC3130PBKLOW-PROFILEQUAD | PCI HOT PLUG CONTROLLER |

| HPC43100VHG30 | 16-Bit Microcontroller |

| HPC46003E20 | 16-Bit Microcontroller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HPC3130APBM | 功能描述:外圍驅(qū)動(dòng)器與原件 - PCI HOT PLUG CONTROLLER RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| HPC3130APBMQUADFLAT | 制造商:TI 制造商全稱(chēng):Texas Instruments 功能描述:PCI HOT PLUG CONTROLLER |

| HPC3130APGE | 功能描述:外圍驅(qū)動(dòng)器與原件 - PCI HOT PLUG CONTROLLER RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| HPC3130APGEG4 | 功能描述:外圍驅(qū)動(dòng)器與原件 - PCI HOT PLUG CONTROLLER RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| HPC3130APGELOW-PROFILEQUA | 制造商:TI 制造商全稱(chēng):Texas Instruments 功能描述:PCI HOT PLUG CONTROLLER |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。