- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370626 > HM62256BLTM-7UL (Hitachi,Ltd.) Triple 3-Input Positive-AND Gates 14-CFP -55 to 125 PDF資料下載

參數(shù)資料

| 型號(hào): | HM62256BLTM-7UL |

| 廠商: | Hitachi,Ltd. |

| 英文描述: | Triple 3-Input Positive-AND Gates 14-CFP -55 to 125 |

| 中文描述: | 256k的SRAM(32 KWord的× 8位) |

| 文件頁數(shù): | 12/20頁 |

| 文件大小: | 154K |

| 代理商: | HM62256BLTM-7UL |

HM62256B Series

12

Low V

CC

Data Retention Characteristics

(Ta = 0 to 70

°

C)

Parameter

Symbol

Min

Typ

*

1

Max

Unit

Test conditions*

6

CS

≥

V

CC

– 0.2 V,

Vin

≥

0V

V

CC

= 3.0 V, Vin

≥

0V

CS

≥

V

CC

– 0.2 V

V

CC

for data retention

V

DR

2.0

—

5.5

V

Data retention current

I

CCDR

—

0.05

30*

2

μ

A

I

CCDR

I

CCDR

t

CDR

—

0.05

10*

3

μ

A

μ

A

—

0.05

3*

4

Chip deselect to data

retention time

0

—

—

ns

See retention Waveform

Operation recovery time

Notes: 1. Typical values are at V

CC

= 3.0 V, Ta = +25

°

C and not guaranteed.

2. 10

μ

A max. at Ta = 0 to +40

°

C.

3. This characteristic is guaranteed only for L-SL version, 3

μ

A max. at Ta = 0 to +40

°

C.

4. This characteristic is guaranteed only for L-UL version, 0.6

μ

A max. at Ta = 0 to +40

°

C.

5. t

RC

= Read cycle time.

6.

CS

controls address buffer,

WE

buffer,

OE

buffer, and Din buffer. If

CS

controls data retention

mode, Vin levels (address,

WE

,

OE

, I/O) can be in the high impedance state.

t

R

t

RC

*

5

—

—

ms

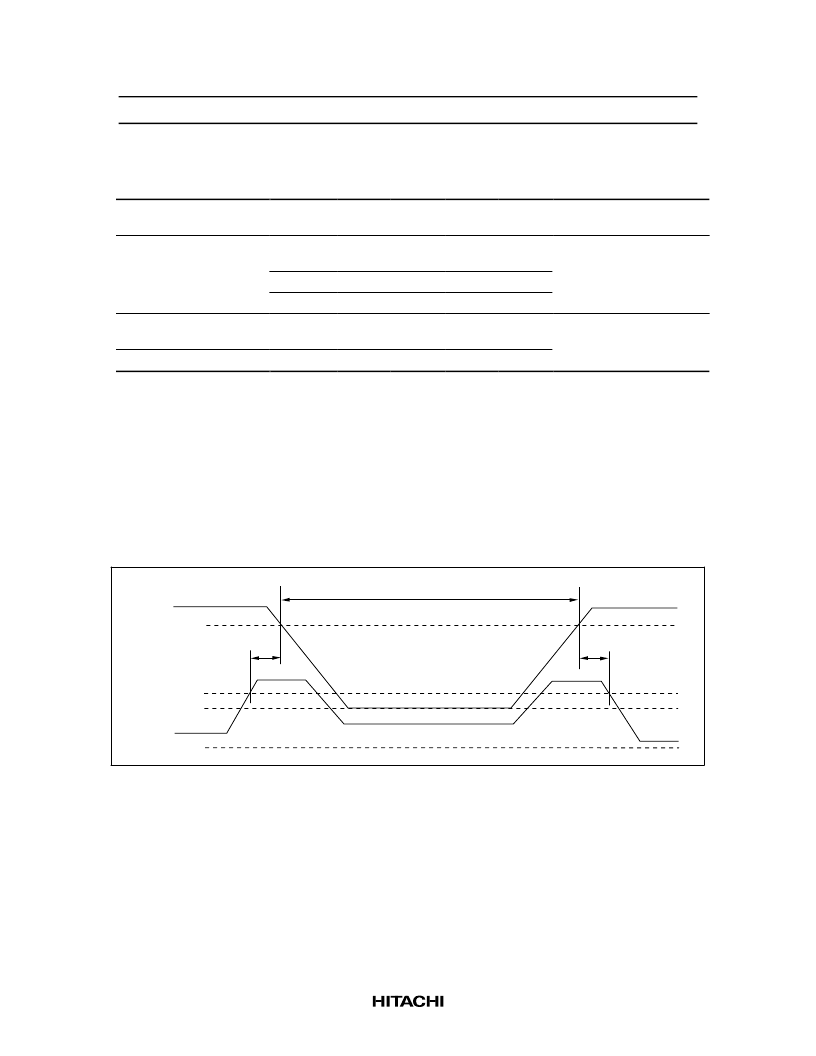

Low V

CC

Data Retention Timing Waveform

V

CC

V

DR

CS

Data retention mode

t

R

4.5V

2.2V

0V

CS

≥

V

CC

0.2V

t

CDR

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HM62256BLTM-8 | Dual J-K Negative-Edge-Triggered Flip-Flops With Preset And Clear 16-CDIP -55 to 125 |

| HM62256BLFP-5SLT | 256k SRAM (32-kword x 8-bit) |

| HM62256BLFP-7SLT | 256k SRAM (32-kword x 8-bit) |

| HM62256BLFP-7T | 256k SRAM (32-kword x 8-bit) |

| HM62256BLFP-7ULT | 256k SRAM (32-kword x 8-bit) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HM62256BLTM-8 | 制造商:HITACHI 制造商全稱:Hitachi Semiconductor 功能描述:256k SRAM (32-kword x 8-bit) |

| HM62256BSERIES | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:IC-256K CMOS SRAM |

| HM62256FP10T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 SRAM |

| HM62256FP-12T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 SRAM |

| HM62256FP-15T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 SRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。