- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371815 > HI7191IB (INTERSIL CORP) 24-Bit, High Precision, Sigma Delta A/D Converter PDF資料下載

參數(shù)資料

| 型號: | HI7191IB |

| 廠商: | INTERSIL CORP |

| 元件分類: | ADC |

| 英文描述: | 24-Bit, High Precision, Sigma Delta A/D Converter |

| 中文描述: | 1-CH 24-BIT DELTA-SIGMA ADC, SERIAL ACCESS, PDSO20 |

| 封裝: | PLASTIC, MS-013AC, SOIC-20 |

| 文件頁數(shù): | 19/24頁 |

| 文件大?。?/td> | 187K |

| 代理商: | HI7191IB |

1915

Control Register

The Control Register contains 24-bits to control the various

sections of the HI7191. This register is a read/write

register.

DC

- Bit 23 is the Data Coding Bit used to select between

two’s complementary and offset binary data coding. When

this bit is set (DC = 1) the data in the Data Output Register

will be two’s complement. When cleared (DC = 0) this data

will be offset binary. When operating in the unipolar mode

the output data is available in straight binary only (the DC bit

is ignored). This bit is cleared after a RESET is applied to

the part.

FP10 through FP0

- Bits 22 through 12 are the Filter pro-

gramming bits that determine the frequency response of the

digital filter. These bits determine the filter cutoff frequency,

the position of the first notch and the data rate of the HI7191.

The first notch of the filter is equal to the decimation rate and

can be determined by the formula:

f

NOTCH

= f

OSC

/(512 x CODE)

where CODE is the decimal equivalent of the value in FP10

through FP0. The values that can be programmed into these

bits are 10 to 2047 decimal, which allows a conversion rate

range of 9.54Hz to 1.953kHz when using a 10MHz clock.

Changing the filter notch frequency, as well as the selected

gain, impacts resolution. The output data rate (or effective

conversion time) for the device is equal to the frequency

selected for the first notch to the filter. For example, if the first

notch of the filter is selected at 50Hz then a new word is avail-

able at a 50Hz rate or every 20ms. If the first notch is at 1kHz

a new word is available every 1ms.

The settling-time of the converter to a full scale step input

change is between 3 and 4 times the data rate. For example,

with the first filter notch at 50Hz, the worst case settling time to

a full scale step input change is 80ms. If the first notch is 1kHz,

the settling time to a full scale input step is 4ms maximum.

The -3dB frequency is determined by the programmed first

notch frequency according to the relationship:

f

-3dB

= 0.262 x f

NOTCH

.

MD2 through MD0

- Bits 11 through 9 are the Operational

Modes of the converter. See Table 4 for the Operational

Modes description. After a RESET is applied to the part these

bits are set to the self calibration mode.

B/U

- Bit 8 is the Bipolar/Unipolar select bit. When this bit is

set the HI7191 is configured for bipolar operation. When this

bit is reset the part is in unipolar mode. This bit is set after a

RESET is applied to the part.

G2 through G0

- Bits 7 through 5 select the gain of the input

analog signal. The gain is accomplished through a program-

mable gain instrumentation amplifier that gains up incoming

signals from 1 to 8. This is achieved by using a switched

capacitor voltage multiplier network preceding the modulator.

The higher gains (i.e., 16 to 128) are achieved through a com-

bination of a PGIA gain of 8 and a digital multiply after the dig-

ital filter (see Table 7). The gain will affect noise and Signal to

Noise Ratio of the conversion. These bits are cleared to a gain

of 1 (G2, G1, G0 = 000) after a RESET is applied to the part.

THREE-STATE

THREE-STATE

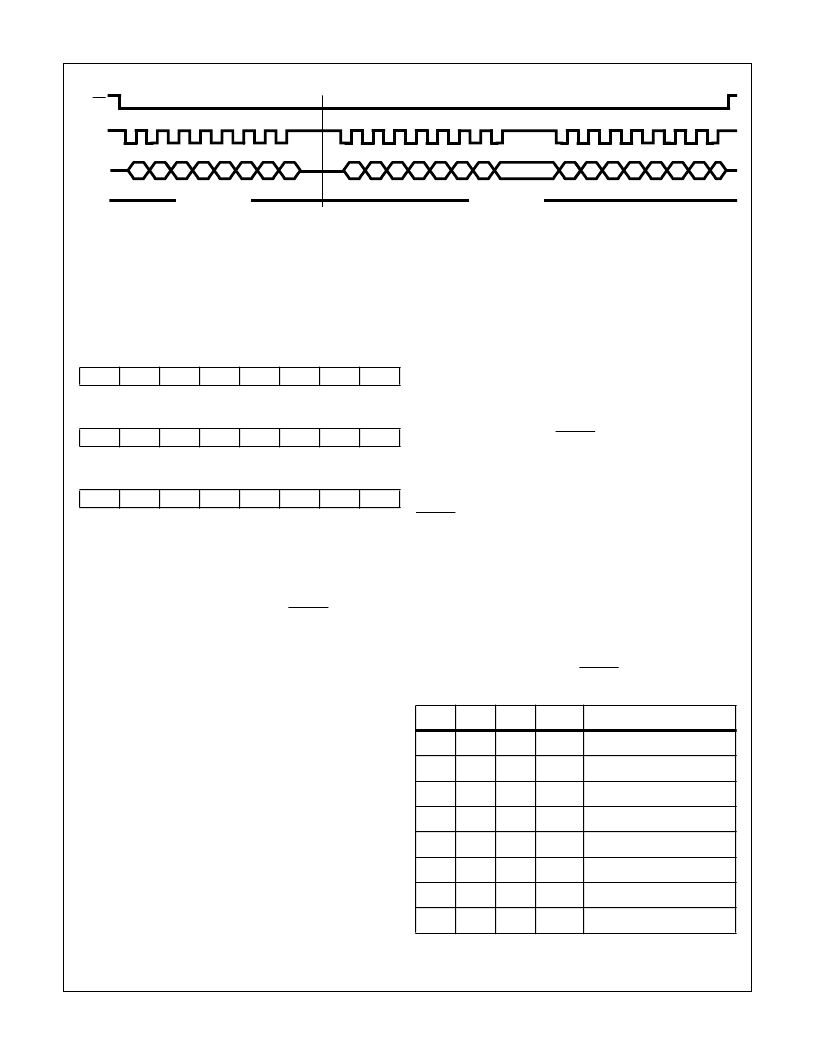

IR WRITE PHASE

DATA TRANSFER PHASE - TWO-BYTE READ

CS

SCLK

SDIO

SDO

I0

I1

I2

I3

I4

I5

I6

I7

B0

B1

B2

B3

B4

B5

B6

B7

B8

B9

B10

B11 B12

B13

B14

B15

FIGURE 19. DATA READ CYCLE, 2-WIRE CONFIGURATION, SCLK IDLE HIGH

BYTE 2

MSB

22

21

20

19

18

17

16

DC

FP10

FP9

FP8

FP7

FP6

FP5

FP4

BYTE 1

15

14

13

12

11

10

9

8

FP3

FP2

FP1

FP0

MD2

MD1

MD0

B/U

BYTE 0

7

6

5

4

3

2

1

LSB

G2

G1

G0

BO

SB

BD

MSB

SDL

TABLE 7. GAIN SELECT BITS

G2

G1

G0

GAIN

GAIN ACHIEVED

0

0

0

1

PGIA = 1, Filter Multiply = 1

0

0

1

2

PGIA = 2, Filter Multiply = 1

0

1

0

4

PGIA = 4, Filter Multiply = 1

0

1

1

8

PGIA = 8, Filter Multiply = 1

1

0

0

16

PGIA = 8, Filter Multiply = 2

1

0

1

32

PGIA = 8, Filter Multiply = 4

1

1

0

64

PGIA = 8, Filter Multiply = 8

1

1

1

128

PGIA = 8, Filter Multiply = 16

HI7191

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HI7191 | 24-Bit, High Precision, Sigma Delta A/D Converter |

| HI7191IP | 24-Bit, High Precision, Sigma Delta A/D Converter |

| HI8182C | Telecommunication IC |

| HI8182CM | Telecommunication IC |

| HI8182R | Telecommunication IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HI7191IBZ | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC ADC 24BIT SIGMADELTA 20 IND RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| HI7191IBZ-T | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC ADC 24BIT SIGMADELTA 20 IND RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| HI7191IP | 功能描述:IC ADC 24BIT PROGBL SER 20-PDIP RoHS:否 類別:集成電路 (IC) >> 數(shù)據(jù)采集 - 模數(shù)轉(zhuǎn)換器 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:2,500 系列:- 位數(shù):12 采樣率(每秒):3M 數(shù)據(jù)接口:- 轉(zhuǎn)換器數(shù)目:- 功率耗散(最大):- 電壓電源:- 工作溫度:- 安裝類型:表面貼裝 封裝/外殼:SOT-23-6 供應(yīng)商設(shè)備封裝:SOT-23-6 包裝:帶卷 (TR) 輸入數(shù)目和類型:- |

| HI7191IPZ | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC W/ANNEAL ADC 24BIT SIGMADELTA 20PDIP RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| HI73127 | 制造商:Hanna 功能描述:Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。