- 您現在的位置:買賣IC網 > PDF目錄384403 > HFA3860IV (HARRIS SEMICONDUCTOR) 11 Mbps Direct Sequence Spread Spectrum Baseband Processor PDF資料下載

參數資料

| 型號: | HFA3860IV |

| 廠商: | HARRIS SEMICONDUCTOR |

| 元件分類: | 無繩電話/電話 |

| 英文描述: | 11 Mbps Direct Sequence Spread Spectrum Baseband Processor |

| 中文描述: | TELECOM, CELLULAR, BASEBAND CIRCUIT, PQFP48 |

| 文件頁數: | 8/40頁 |

| 文件大?。?/td> | 250K |

| 代理商: | HFA3860IV |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁當前第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

4-8

RX Port

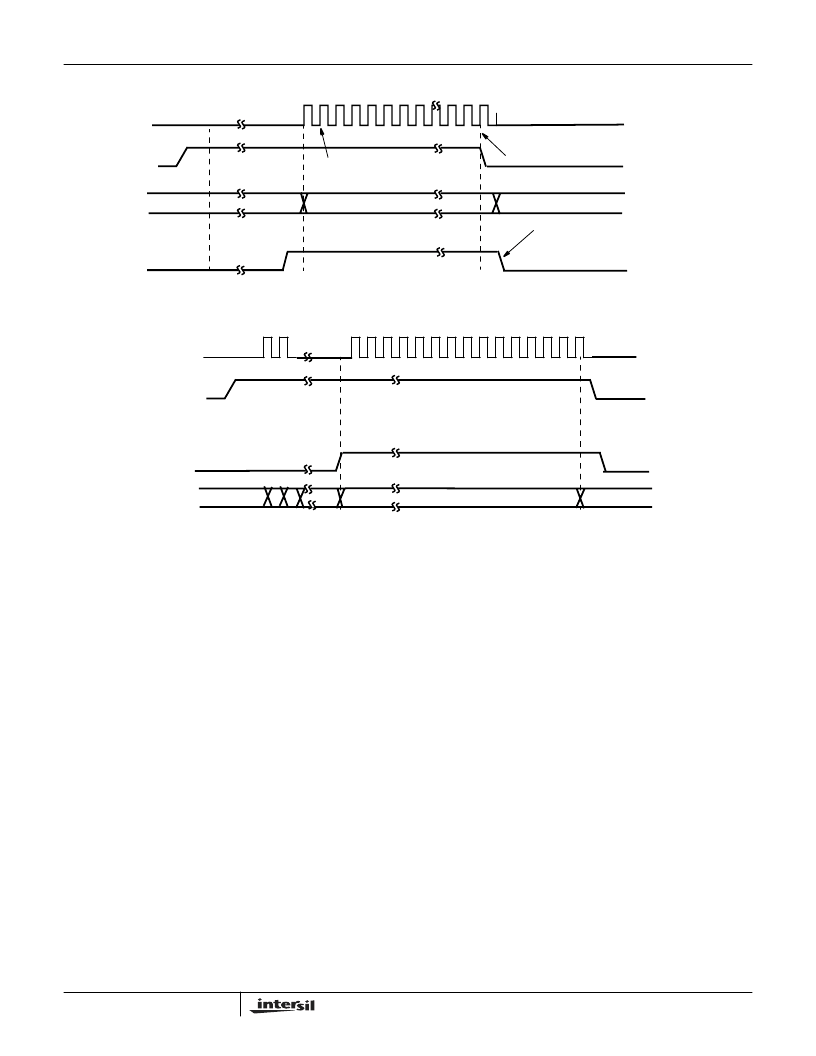

The timing diagram Figure 5 illustrates the relationships

between the various signals of the RX port. The receive data

port serially outputs the demodulated data from RXD. The

data is output as soon as it is demodulated by the HFA3860.

RX_PE must be at its active state throughout the receive

operation. When RX_PE is inactive the device's receive

functions, including acquisition, will be in a stand by mode.

RXCLK is an output from the HFA3860 and is the clock for

the serial demodulated data on RXD. MD_RDY is an output

from the HFA3860 and it may be set to go active after SFD

or CRC fields. Note that RXCLK becomes active after the

Start Frame Delimiter (SFD) to clock out the Signal,

Service, and Length fields, then goes inactive during the

header CRC field. RXCLK becomes active again for the

MPDU. MD_RDY returns to its inactive state after RX_PE is

deactivated by the external controller, or if a header error is

detected. A header error is either a failure of the CRC

check, or the failure of the received signal field to match

one of the 4 programmed signal fields. For either type of

header error, the HFA3860 will reset itself after reception of

the CRC field. If MD_RDY had been set to go active after

CRC, it will remain low.

MD_RDY and RXCLK can be configured through CR 1, bit 6-7

to be active low, or active high. The receive port is completely

independent from the operation of the other interface ports

including the TX port, supporting therefore a full duplex mode.

I/Q A/D Interface

The PRISM baseband processor chip (HFA3860) includes

two 3-bit Analog to Digital converters (A/Ds) that sample the

analog input from the IF down converter. The I/Q A/D clock,

samples at twice the chip rate. The nominal sampling rate is

22MHz.

The interface specifications for the I and Q A/Ds are listed in

Table 2.

LSB

DATA PACKET

MSB

DEASSERTED WHEN LAST

CHIP OF MPDU CLEARS

MOD PATH OF 3860

TXCLK

TX_PE

TXD

TX_RDY

NOTE: Preamble/Header and Data is transmitted LSB first. TXD shown generated from rising edge of TXCLK.

FIGURE 4. TX PORT TIMING

FIRST DATA BIT SAMPLED

LAST DATA BIT SAMPLED

RXCLK

RX_PE

MD_RDY

RXD

PROCESSING

PREAMBLE/HEADER

LSB

DATA

MSB

NOTE:

MD_RDY active after CRC16. See detailed timing diagrams on page 35.

FIGURE 5. RX PORT TIMING

HEADER

FIELDS

MPDU DATA

HFA3860

相關PDF資料 |

PDF描述 |

|---|---|

| HFA3860IV96 | 11 Mbps Direct Sequence Spread Spectrum Baseband Processor |

| HFA3861A | Direct Sequence Spread Spectrum Baseband Processor(直接序列擴頻基帶處理器) |

| HFA3861B | Direct Sequence Spread Spectrum Baseband Processor(直接序列擴譜基帶處理器) |

| HFA3861 | Direct Sequence Spread Spectrum (DSSS) baseband processor(直接序列擴頻基帶處理器) |

| HFA3861IV | Direct Sequence Spread Spectrum Baseband Processor |

相關代理商/技術參數 |

參數描述 |

|---|---|

| HFA3860IV WAF | 制造商:Harris Corporation 功能描述: |

| HFA3860IV96 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:11 Mbps Direct Sequence Spread Spectrum Baseband Processor |

| HFA3861 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Direct Sequence Spread Spectrum Baseband Processor |

| HFA3861A | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Direct Sequence Spread Spectrum Baseband Processo |

| HFA3861AIN | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Direct Sequence Spread Spectrum Baseband Processo |

發(fā)布緊急采購,3分鐘左右您將得到回復。