- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384403 > HFA3860IV (HARRIS SEMICONDUCTOR) 11 Mbps Direct Sequence Spread Spectrum Baseband Processor PDF資料下載

參數(shù)資料

| 型號: | HFA3860IV |

| 廠商: | HARRIS SEMICONDUCTOR |

| 元件分類: | 無繩電話/電話 |

| 英文描述: | 11 Mbps Direct Sequence Spread Spectrum Baseband Processor |

| 中文描述: | TELECOM, CELLULAR, BASEBAND CIRCUIT, PQFP48 |

| 文件頁數(shù): | 27/40頁 |

| 文件大小: | 250K |

| 代理商: | HFA3860IV |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁當前第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

4-27

Control Registers

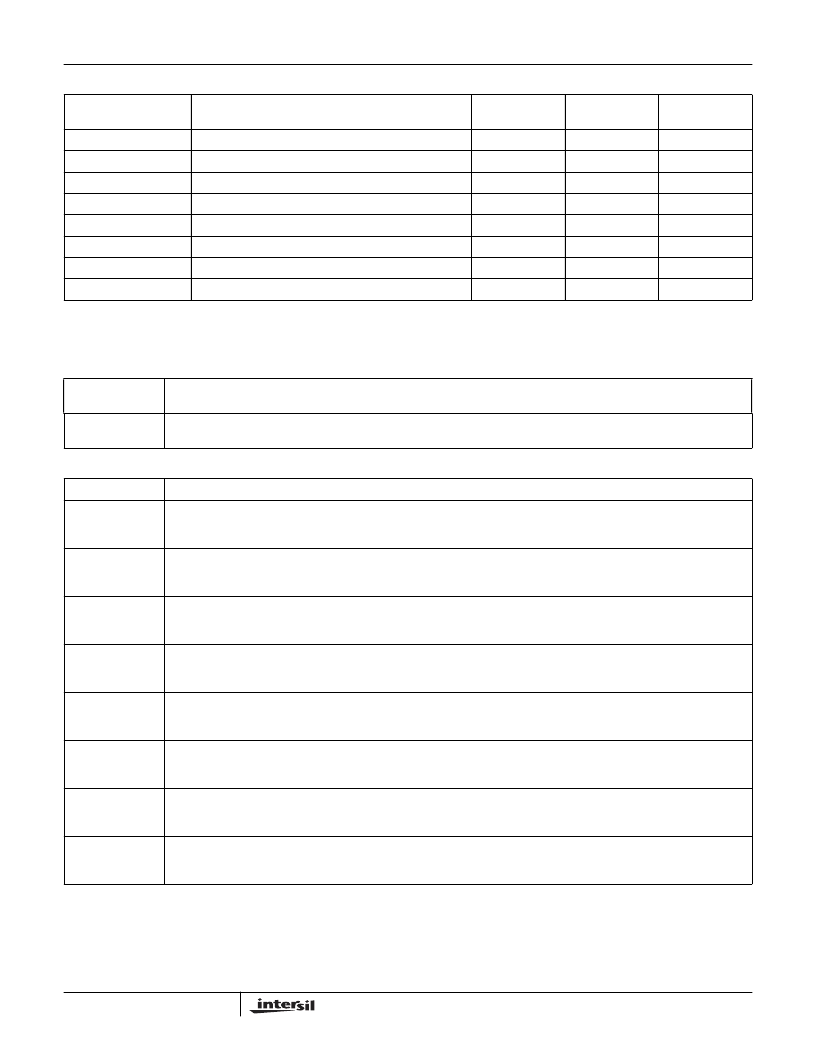

The following tables describe the function of each control register along with the associated bits in each control register.

CR24

RX Status

R

60

X

CR25

RX service Field Status

R

64

X

CR26

RX Length Field status (high)

R

68

X

CR27

RX Length Field status (low)

R

6C

X

CR28

Test Bus Address

R/W

70

00

CR29

Test Bus Monitor

R

74

X

CR30

Test Register 1

R/W

78

00

CR31

Test Register 2

R/W

7C

02

TABLE 11. CONTROL REGISTER VALUES FOR SINGLE ANTENNA ACQUISITION (Continued)

CONFIGURATION

REGISTER

NAME

TYPE

REGISTER

ADDRESS HEX

1/2/5.5/11 MBps

CONFIGURATION REGISTER 0 ADDRESS (0h) PART/VERSION CODE

Bit 7:4

Part Code

0 = HFA3860

Bit 3:0

Version Code

1 = First Version

CONFIGURATION REGISTER 1 ADDRESS (04h) I/O POLARITY

This register is used to define the phase of clocks and other interface signals. 00h is normal setting.

Bit 7

This controls the phase of the RX_CLK output

Logic 1 = Invert Clk

Logic 0 = Non-Inverted Clk

Bit 6

This control bit selects the active level of the MD_RDY output pin 34.

Logic 1 = MD_RDY is Active 0

Logic 0 = MD_RDY is Active 1

Bit 5

This control bit selects the active level of the Clear Channel Assessment (CCA) output pin 32.

Logic 1 = CCA Active 1

Logic 0 = CCA Active 0

Bit 4

This control bit selects the active level of the Energy Detect (ED) output which is an output pin at the test port, pin 44.

Logic 1 = ED Active 0

Logic 0 = ED Active 1

Bit 3

This control bit selects the active level of the Carrier Sense (CRS) output pin which is an output pin at the test port, pin 45.

Logic 1 = CRS Active 0

Logic 0 = CRS Active 1

Bit 2

This control bit selects the active level of the transmit enable (TX_PE) input pin 2.

Logic 1 = TX_PE Active 0

Logic 0 = TX_PE Active 1

Bit 1

This control bit selects the phase of the transmit output clock (TXCLK) pin 4.

Logic 1 = Inverted TXCLK

Logic 0 = NON-Inverted TXCLK

Bit 0

This control bit selects the active level of the transmit ready (TX_RDY) output pin 5.

Logic 1 = TX_RDY active 0

Logic 0 = TX_RDY active 1

HFA3860

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HFA3860IV96 | 11 Mbps Direct Sequence Spread Spectrum Baseband Processor |

| HFA3861A | Direct Sequence Spread Spectrum Baseband Processor(直接序列擴頻基帶處理器) |

| HFA3861B | Direct Sequence Spread Spectrum Baseband Processor(直接序列擴譜基帶處理器) |

| HFA3861 | Direct Sequence Spread Spectrum (DSSS) baseband processor(直接序列擴頻基帶處理器) |

| HFA3861IV | Direct Sequence Spread Spectrum Baseband Processor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HFA3860IV WAF | 制造商:Harris Corporation 功能描述: |

| HFA3860IV96 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:11 Mbps Direct Sequence Spread Spectrum Baseband Processor |

| HFA3861 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Direct Sequence Spread Spectrum Baseband Processor |

| HFA3861A | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Direct Sequence Spread Spectrum Baseband Processo |

| HFA3861AIN | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Direct Sequence Spread Spectrum Baseband Processo |

發(fā)布緊急采購,3分鐘左右您將得到回復。