- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370464 > HD61830A00H (Hitachi,Ltd.) LCDC (LCD Timing Controller) PDF資料下載

參數(shù)資料

| 型號: | HD61830A00H |

| 廠商: | Hitachi,Ltd. |

| 英文描述: | LCDC (LCD Timing Controller) |

| 中文描述: | LCDC(LCD定時控制器) |

| 文件頁數(shù): | 25/43頁 |

| 文件大?。?/td> | 173K |

| 代理商: | HD61830A00H |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁當(dāng)前第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁

HD61830/HD61830B

25

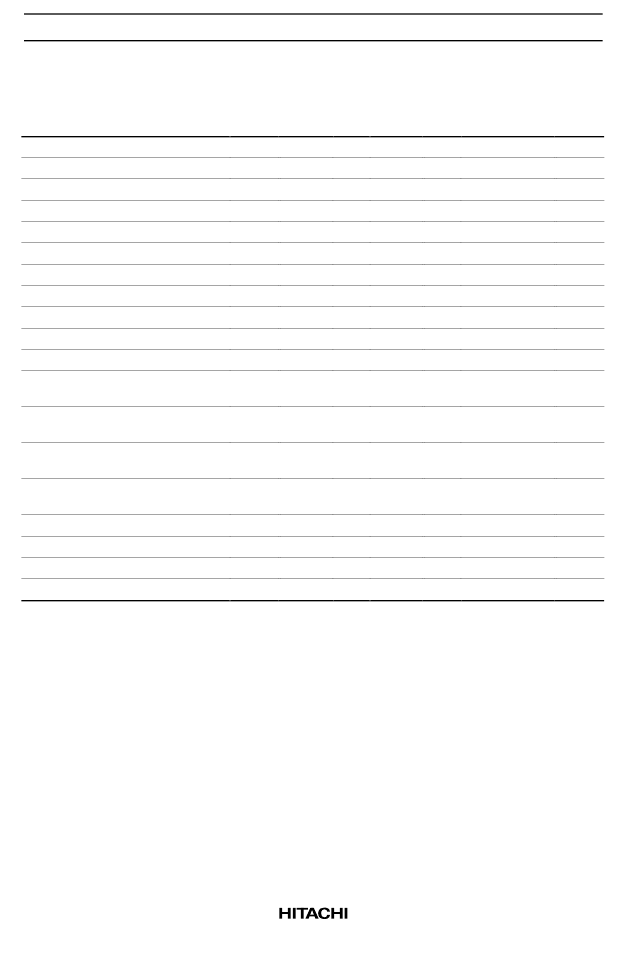

HD61830 Electrical Characteristics (V

CC

= 5 V

±

10%, GND = 0 V, T

a

= –20 to

+75

°

C)

Item

Symbol Min

Typ

Max

Unit

Test Condition Notes

Input high voltage (TTL)

VIH

2.2

—

V

CC

0.8

V

1

Input low voltage (TTL)

VIL

0

—

V

2

Input high voltage

VIHR

3.0

—

V

CC

V

CC

0.3 V

CC

V

CC

0.4

V

3

Input high voltage (CMOS)

VIHC

0.7 V

CC

0

—

V

4

Input low voltage (CMOS)

VILC

—

V

4

Output high voltage (TTL)

VOH

2.4

—

V

–I

OH

= 0.6 mA

I

OL

= 1.6 mA

–I

OH

= 0.6 mA

I

OL

= 0.6 mA

VIN = 0 – V

CC

VOUT = 0 – V

CC

8

CR oscillation

f

osc

= 500 kHz

External clock

f

cp

= 1 MHz

C

f

= 15 pF

±

5%

R

f

= 39 k

±

2%

5

Output low voltage (TTL)

VOL

0

—

V

5

Output high voltage (CMOS)

VOHC

V

CC

– 0.4 —

0

V

CC

0.4

V

6

Output low voltage (CMOS)

VOLC

—

V

6

Input leakage current

I

IN

I

TSL

P

W

1

–5

—

5

μ

A

μ

A

7

Three-state leakage current

–10

—

10

Power dissipation (1)

—

10

15

mW

9

Power dissipation (2)

P

W

2

—

20

30

mW

9

Internal clock operation

(Clock oscillation frequency)

f

osc

400

500

600

kHz

10

External clock operation

(External clock operating frequency)

f

cp

100

500

1100

kHz

11

External clock duty

Duty

47.5

50

52.5

%

11

External clock rise time

t

rcp

t

fcp

I

PL

—

—

0.05

μ

s

μ

s

μ

A

11

External clock fall time

—

—

0.05

11

Pull-up current

Notes: The I/O terminals have the following configuration:

1. Applied to input terminals and I/O common terminals, except terminals

SYNC

, CR, and

RES

.

2. Applied to input terminals and I/O common terminals, except terminals

SYNC

and CR.

3. Applied to terminal

RES

.

4. Applied to terminals

SYNC

and CR.

5. Applied to terminals DB0–DB7,

WE

, MA0–MA15, and MD0–MD7.

6. Applied to terminals

SYNC

, CP0, FLM, CL1, CL2, D1, D2, MA, and MB.

7. Applied to input terminals.

8. Applied to I/O common terminals. However, the current which flows into the output drive MOS is

excluded.

2

10

20

VIN = GND

12

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HD61830 | LCDC (LCD Timing Controller) |

| HD61830B | LCDC (LCD Timing Controller) |

| HD61830B00H | LCDC (LCD Timing Controller) |

| HD6301X0 | CMOS MCU |

| HD6301X0CP | CMOS MCU |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HD61830B | 制造商:HITACHI 制造商全稱:Hitachi Semiconductor 功能描述:LCDC (LCD Timing Controller) |

| HD61830B00 | 制造商:HITCHI 功能描述: |

| HD61830B00H | 制造商:HITACHI 制造商全稱:Hitachi Semiconductor 功能描述:LCDC (LCD Timing Controller) |

| HD61945MP | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog Phase-Locked Loop |

| HD6301V0P | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。