- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370400 > GTLP6C817MTC (FAIRCHILD SEMICONDUCTOR CORP) Low Drive GTLP-to-LVTTL 1:6 Clock Driver PDF資料下載

參數(shù)資料

| 型號: | GTLP6C817MTC |

| 廠商: | FAIRCHILD SEMICONDUCTOR CORP |

| 元件分類: | 時鐘及定時 |

| 英文描述: | Low Drive GTLP-to-LVTTL 1:6 Clock Driver |

| 中文描述: | GTLP SERIES, LOW SKEW CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO24 |

| 封裝: | 4.40 MM, MO-153, TSSOP-24 |

| 文件頁數(shù): | 5/7頁 |

| 文件大?。?/td> | 64K |

| 代理商: | GTLP6C817MTC |

5

www.fairchildsemi.com

G

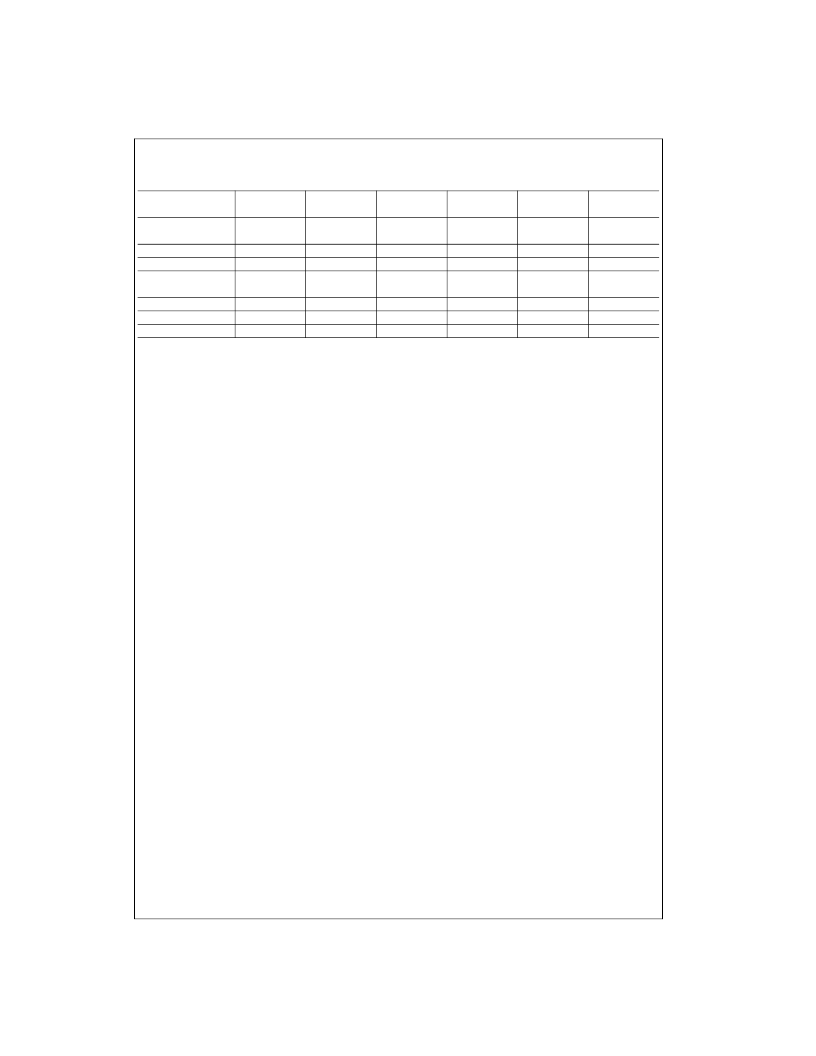

Extended Electrical Characteristics

Over recommended ranges of supply voltage and operating free-air temperature V

REF

=

1.0V (unless otherwise noted).

C

L

=

30 pF for B Port and C

L

=

50 pF for A Port

From

To

(Input)

(Output)

t

OSLH

(Note 8)

A

B

t

OSHL

(Note 8)

A

B

t

PS

(Note 9)

A

B

t

PV(HL)

(Note 10)(Note 11)

A

B

t

OSLH

(Note 8)

B

A

t

OSHL

(Note 8)

B

A

t

OST

(Note 8)

B

A

t

PS

(Note 9)

B

A

t

PV

(Note 10)

B

A

Note 7:

All typical values are at V

CC

=

3.3 V and T

A

=

25

°

C.

Note 8:

t

OSHL

/t

OSLH

and t

OST

–

Output-to-Output skew is defined as the absolute value of the difference between the actual propagation delay for all outputs

within the same packaged device. The specifications are given for specific worst case V

CC

and temperature and apply to any outputs switching in the same

direction dither HIGH-to-LOW (t

OSHL

) or LOW-to-HIGH (t

OSLH

) or in opposite directions both HL and LH (t

OST

). This parameter is guaranteed by design and

statistical process distribution. Actual skew values between the GTLP outputs could vary on the backplane due to the loading and impedance seen by the

device.

Note 9:

t

PS

–

Pin or Transition skew is defined as the difference between the LOW-to-HIGH transition and the HIGH-to-LOW transition on the same pin. The

parameter is measured across all the outputs of the same chip is specified for a specific worst case V

CC

and temperature. This parameter is guaranteed by

design and statistical process distribution. Actual skew values between the GTLP outputs could vary on the backplane due to the loading and impedance

seen by the device.

Note 10:

t

PV

–

Part-to-Part skew is defined as the absolute value of the difference between the actual propagation delay for all outputs from device-to-device.

The parameter is specified for a specific worst case V

CC

and temperature. This parameter is guaranteed by design and statistical process distribution. Actual

skew values between the GTLP output could vary on the backplane due to the loading and impedance seen by the device.

Note 11:

Due to the open drain structure on GTLP outputs t

OST

and t

PV(LH)

in the A-to-B direction are not specified. Skew on these paths is dependent on the

V

TT

and R

T

values on the backplane.

Symbol

Min

Typ

Max

Units

(Note 7)

0.1

0.1

0.3

0.2

0.6

1.0

ns

ns

1.3

0.7

0.4

ns

0.1

0.1

ns

0.2

0.1

1.1

1.0

ns

ns

2.4

ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GTLP8T306MTCX | Single 8-bit Bus Transceiver |

| GTLP8T306MTC | 8-Bit LVTTL/GTLP Bus Transceiver |

| GTLPH16612DGG | 18-Bit Bus Transceiver |

| GTLPH16612DL | 18-Bit Bus Transceiver |

| GTL | |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| GTLP6C817MTCX | 功能描述:時鐘緩沖器 1:6 Clock Driver RoHS:否 制造商:Texas Instruments 輸出端數(shù)量:5 最大輸入頻率:40 MHz 傳播延遲(最大值): 電源電壓-最大:3.45 V 電源電壓-最小:2.375 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LLP-24 封裝:Reel |

| GTLP75X1800 | 制造商:HellermannTyton 功能描述:Low profile Grip Tie roll - .5 wide - Black |

| GTLP8T306 | 制造商:FAIRCHILD 制造商全稱:Fairchild Semiconductor 功能描述:8-Bit LVTTL/GTLP Bus Transceiver |

| GTLP8T306MTC | 功能描述:總線收發(fā)器 8-Bit Bus Trans RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

| GTLP8T306MTCX | 功能描述:總線收發(fā)器 8-Bit Bus Trans RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。