- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370389 > GS84118B-166 x18 Synchronous SRAM PDF資料下載

參數(shù)資料

| 型號: | GS84118B-166 |

| 英文描述: | x18 Synchronous SRAM |

| 中文描述: | x18同步SRAM |

| 文件頁數(shù): | 24/30頁 |

| 文件大?。?/td> | 584K |

| 代理商: | GS84118B-166 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當前第24頁第25頁第26頁第27頁第28頁第29頁第30頁

Rev: 1.05 7/2001

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

24/30

1999, Giga Semiconductor, Inc.

GS84118T/B-166/150/130/100

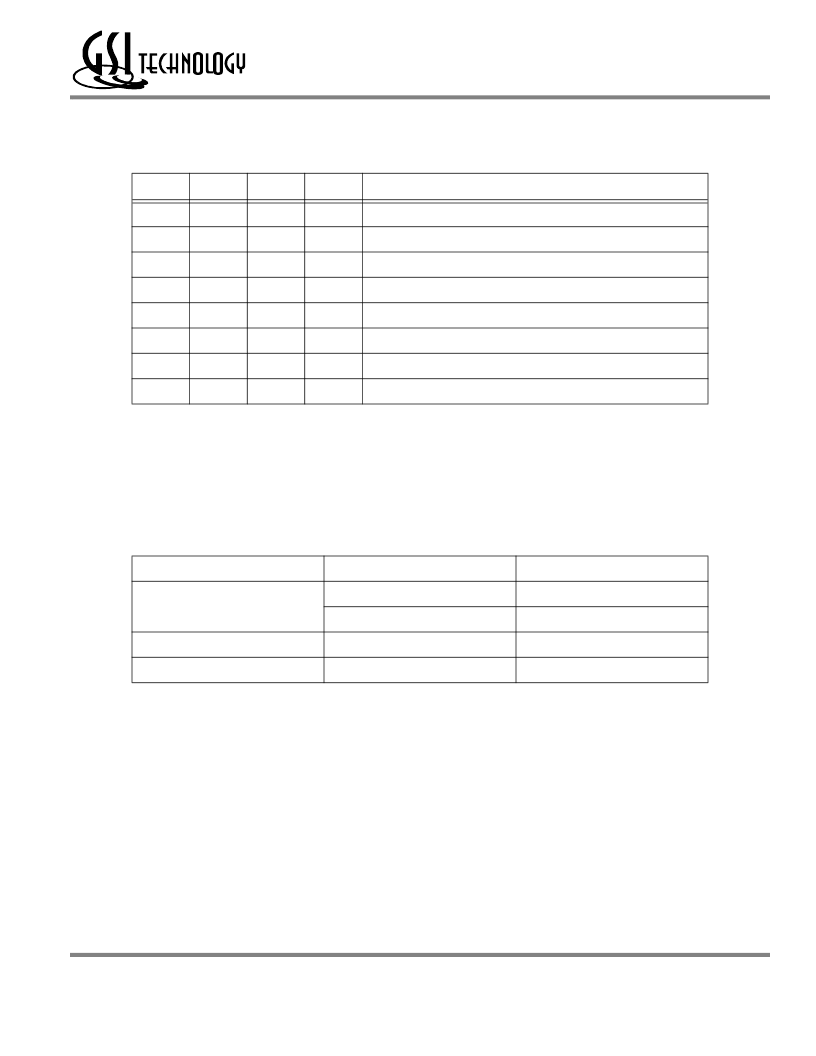

Instruction Register (3 Bits)

The JTAG Instruction register is consisted of shift register stage and parallel output latch. The register is 3 bits wide and is encoded

as follow:

Bypass Register (1 Bit)

The Bypass Register is one bit wide and is connected electrically between TDI and TDO and provides the minimum length serially

path between TDI and TDO.

ID Register (32 Bits)

The ID Register are 32 bits wide and are listed as follow:

Octal

MSB

—

LSB

Instruction

0

0

0

0

Bypass

1

0

0

1

IDCODE—Read device ID

2

0

1

0

Sample-Z—Sample Inputs and tri-state DQs, Match

3

0

1

1

Bypass

4

1

0

0

Sample—Sample Inputs

5

1

0

1

Private—Manufacturer use only

6

1

1

0

Bypass

7

1

1

1

Bypass

Header

ID[0]

1

GSI ID

(89 decimal in bank 2)

ID[7:1]

101 1001

ID[11:8]

0001

Part Number

ID[27:12]

0000 0000 0000 0000

Revision Number

ID[31:28]

xxxx

相關PDF資料 |

PDF描述 |

|---|---|

| GS84118T-100 | x18 Synchronous SRAM |

| GS84118T-133 | x18 Synchronous SRAM |

| GS84118T-150 | x18 Synchronous SRAM |

| GS84118T-166 | x18 Synchronous SRAM |

| GS8550BU | TRANSISTOR | BJT | PNP | 25V V(BR)CEO | 800MA I(C) | TO-226AA |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| GS84118B-166I | 制造商:GSI 制造商全稱:GSI Technology 功能描述:256K x 18 Sync Cache Tag |

| GS84118I-133I | 制造商:GSI 制造商全稱:GSI Technology 功能描述:256K x 18 Sync Cache Tag |

| GS84118T-100 | 制造商:GSI 制造商全稱:GSI Technology 功能描述:256K x 18 Sync Cache Tag |

| GS84118T-100I | 制造商:GSI 制造商全稱:GSI Technology 功能描述:256K x 18 Sync Cache Tag |

| GS84118T-133 | 制造商:GSI 制造商全稱:GSI Technology 功能描述:256K x 18 Sync Cache Tag |

發(fā)布緊急采購,3分鐘左右您將得到回復。