- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370386 > GS8161Z36T-180I x36 Fast Synchronous SRAM PDF資料下載

參數(shù)資料

| 型號: | GS8161Z36T-180I |

| 英文描述: | x36 Fast Synchronous SRAM |

| 中文描述: | x36快速同步SRAM |

| 文件頁數(shù): | 4/24頁 |

| 文件大?。?/td> | 468K |

| 代理商: | GS8161Z36T-180I |

Rev: 2.06 8/2000

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com

4/24

1998, Giga Semconductor, Inc.

Preliminary

GS8160Z18/36T-225/200/180/166/150/133

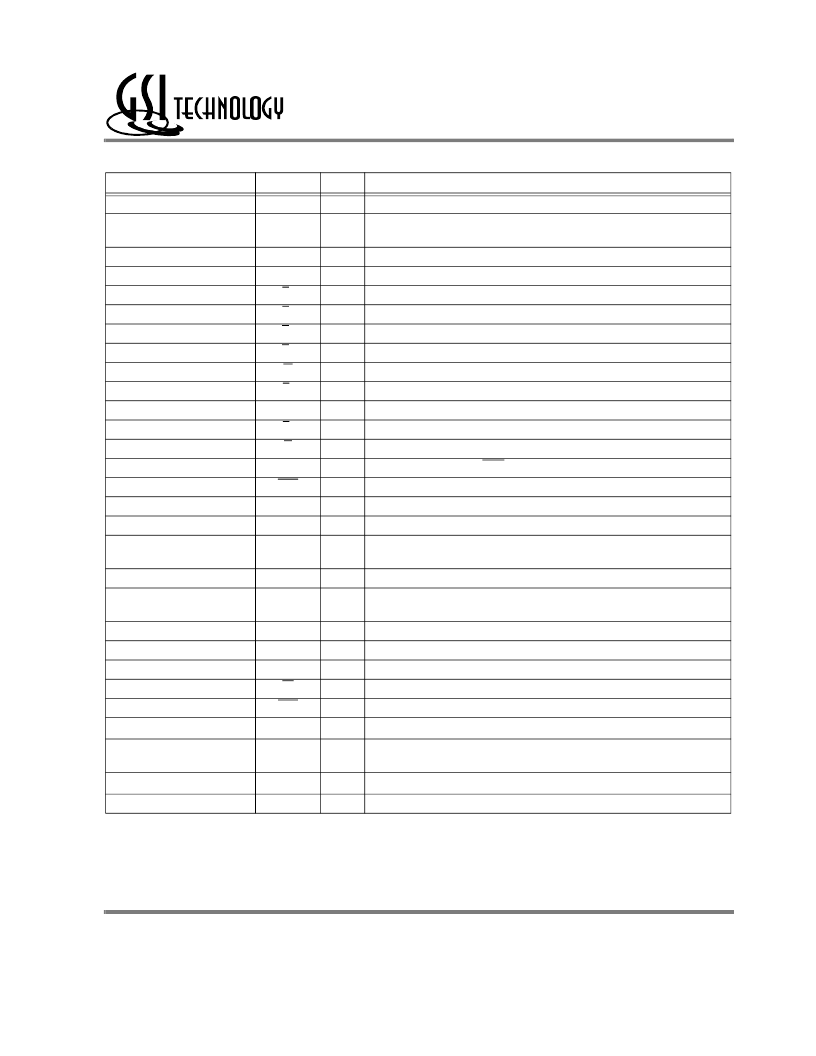

100 Pin TQFP Pin Descriptions

Pin Location

37, 36

35, 34, 33, 32, 100, 99, 84, 83,

82, 81, 44, 45, 46,47, 48, 49, 50

80

89

93

94

95

96

88

98

97

92

86

85

87

58, 59, 62,63, 68, 69, 72, 73, 74 DQ

A1

–

DQ

A9

8, 9, 12, 13, 18, 19, 22, 23, 24

51, 52, 53, 56, 57, 75, 78, 79,

1, 2, 3, 6, 7, 25, 28, 29, 30

51, 52, 53, 56, 57, 58, 59, 62,63 DQ

A1

–

DQ

A9

68, 69, 72, 73, 74, 75,

78, 79, 80

1, 2, 3, 6, 7, 8, 9, 12, 13

18, 19, 22, 23, 24, 25, 28, 29, 30 DQ

D1

–

DQ

D9

64

14

31

Symbol

A

0

, A

1

Type

In

Description

Burst Address Inputs; Preload the burst counter

A

2

–

A

18

In

Address Inputs

A

19

CK

B

A

B

B

B

C

B

D

W

E

1

E

2

E

3

G

ADV

CKE

In

In

In

In

In

In

In

In

In

In

In

In

In

I/O

I/O

Address Input (x18 Version Only)

Clock Input Signal

Byte Write signal for data inputs DQ

A1

-DQ

A9

; active low

Byte Write signal for data inputs DQ

B1

-DQ

B9

; active low

Byte Write signal for data inputs DQ

C1

-DQ

C9

; active low (x36 Versions Only)

Byte Write signal for data inputs DQ

D1

-DQ

D9

; active low (x36 Versions Only)

Write Enable; active low

Chip Enable; active low

Chip Enable; Active High. For self decoded depth expansion

Chip Enable; Active Low. For self decoded depth expansion

Output Enable; active low

Advance/Load; Burst address counter control pin

Clock Input Buffer Enable; active low

Byte A Data Input and Output pins (x18 Version Only)

Byte B Data Input and Output pins (x18 Version Only)

DQ

B1

–

DQ

B9

NC

—

No Connect (x18 Version Only)

I/O

Byte A Data Input and Output pins (x36 Versions Only)

DQ

B1

–

DQ

B9

I/O

Byte B Data Input and Output pins (x36 Versions Only)

DQ

C1

–

DQ

C9

I/O

I/O

In

In

In

Byte C Data Input and Output pins (x36 Versions Only)

Byte D Data Input and Output pins (x36 Versions Only)

Power down control; active high

Pipeline/Flow Through Mode Control; active low

Linear Burst Order; active low

ZZ

FT

LBO

V

DD

15, 16, 41, 65, 91

In

3.3 V power supply

5,10, 17, 21, 26, 40, 55, 60, 67,

71, 76, 90

V

SS

In

Ground

4, 11, 20, 27, 54, 61, 70, 77

V

DDQ

NC

In

3.3 V output power supply for noise reduction

38, 39, 42, 43, 66

—

No Connect

This Material Copyrighted by Its Respective Manufacturer

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GS8161Z36T-180IT | x36 Fast Synchronous SRAM |

| GS8161Z36T-180T | x36 Fast Synchronous SRAM |

| GS81ICA | Peripheral IC |

| GS01ITCA | Peripheral IC |

| GS82032AQ-133T | x32 Fast Synchronous SRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| GS8161Z36T-180IT | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x36 Fast Synchronous SRAM |

| GS8161Z36T-180T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x36 Fast Synchronous SRAM |

| GS8161Z36T-200 | 制造商:GSI 制造商全稱:GSI Technology 功能描述:18Mb Pipelined and Flow Through Synchronous NBT SRAM |

| GS8161Z36T-200I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:18Mb Pipelined and Flow Through Synchronous NBT SRAM |

| GS8161Z36T-200IT | 制造商:GSI 制造商全稱:GSI Technology 功能描述:18Mb Pipelined and Flow Through Synchronous NBT SRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。