- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370366 > GMS81C5032-XXXQ MICROCONTROLLER|8-BIT|CMOS|QFP|44PIN|PLASTIC PDF資料下載

參數(shù)資料

| 型號: | GMS81C5032-XXXQ |

| 英文描述: | MICROCONTROLLER|8-BIT|CMOS|QFP|44PIN|PLASTIC |

| 中文描述: | 單片機| 8位|的CMOS | QFP封裝| 44PIN |塑料 |

| 文件頁數(shù): | 69/93頁 |

| 文件大?。?/td> | 853K |

| 代理商: | GMS81C5032-XXXQ |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁當前第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁

GMS81C1404/GMS81C1408

June. 2001 Ver 1.2

67

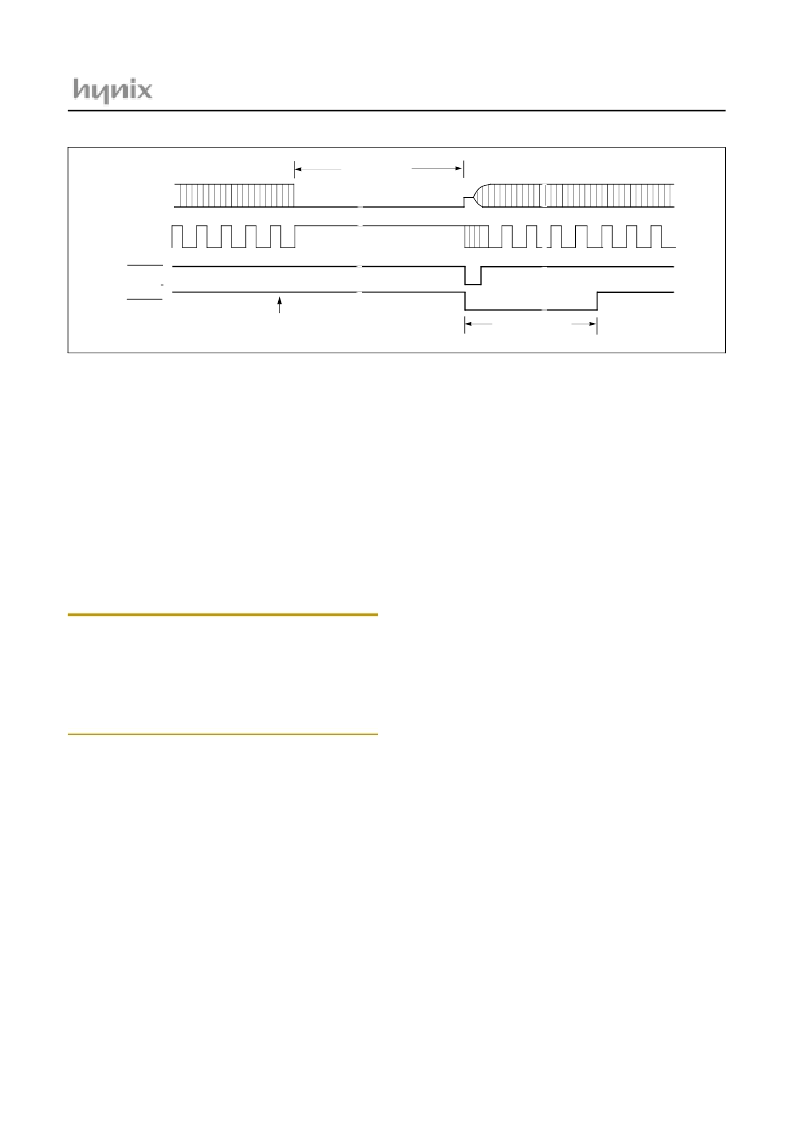

Figure 19-3 Timing of STOP Mode Release by RESET

19.2 STOP Mode using Internal RCWDT

In the STOP mode using Internal RC-Oscillated Watchdog

Timer, the on-chip oscillator is stopped. But internal RC

oscillation circuit is oscillated in this mode. The on-chip

RAM and Control registers are held. The port pins out the

values held by their respective port data register, port di-

rection registers.

The Internal RC-Oscillated Watchdog Timer mode is

activated by execution of STOP instruction after set-

ting the bit RCWDT of CKCTLR to “1”. ( This register

should be written by byte operation. If this register is

set by bit manipulation instruction, for example “set1”

or “clr1” instruction, it may be undesired operation )

Note:

After STOP instruction, at least two or more NOP in-

struction should be written

Ex)

LDM WDTR

,#1111_1111B

LDM CKCTLR

,#00

1

0_1110B

STOP

NOP

NOP

Release the STOP mode using internal RCWDT

The exit from STOP mode using Internal RC-Oscillated

Watchdog Timer is hardware reset or external interrupt.

Reset re-defines all the Control registers but does not

change the on-chip RAM. External interrupts allow both

on-chip RAM and Control registers to retain their values.

If I-flag = 1, the normal interrupt response takes place. In

this case, if the bit WDTON of CKCTLR is set to “0” and

the bit WDTE of IENH is set to “1”, the device will exe-

cute the watchdog timer interrupt service routine.(Figure

19-4 ) However, if the bit WDTON of CKCTLR is set to

“1”, the device will generate the internal RESET signal

and execute the reset processing. (Figure 19-5 )

If I-flag = 0, the chip will resume execution starting with

the instruction following the STOP instruction. It will not

vector to interrupt service routine.( refer to Figure 19-1 )

When exit from STOP mode using Internal RC-Oscillated

Watchdog Timer by external interrupt, the oscillation sta-

bilization time is required to normal operation. Figure 19-

4 shows the timing diagram. When release the Internal

RC-Oscillated Watchdog Timer mode, the basic interval

timer is activated on wake-up. It is increased from 00

H

un-

til FF

H

. The count overflow is set to start normal opera-

tion. Therefore, before STOP instruction, user must be set

its relevant prescaler divide ratio to have long enough time

(more than 20msec). This guarantees that oscillator has

started and stabilized.

By reset, exit from STOP mode using internal RC-Oscillat-

ed Watchdog Timer is shown in Figure 19-5 .

~

STOP Mode

Time can not be control by software

Oscillator

(X

IN

pin)

~

~

~

STOP Instruction Execution

Stabilizing Time

t

ST

= 64mS @4MHz

Internal

Clock

Internal

RESET

~

~

~

~

~

RESET

相關PDF資料 |

PDF描述 |

|---|---|

| GMS81C5032-XXXQT | MICROCONTROLLER|8-BIT|CMOS|QFP|44PIN|PLASTIC |

| GMS81C5032-XXXSK | MICROCONTROLLER|8-BIT|CMOS|DIP|28PIN|PLASTIC |

| GMS81C7208 | NET CENTER 48" W |

| GMS81C7208LQ | 8-BIT SINGLE-CHIP MICROCONTROLLERS |

| GMS81C7208Q | 8-BIT SINGLE-CHIP MICROCONTROLLERS |

相關代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| GMS81C5032-XXXQT | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MICROCONTROLLER|8-BIT|CMOS|QFP|44PIN|PLASTIC |

| GMS81C5032-XXXSK | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MICROCONTROLLER|8-BIT|CMOS|DIP|28PIN|PLASTIC |

| GMS81C5108 | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:HYNIX SEMICONDUCTOR INC. 8-BIT SINGLE-CHIP MICROCONTROLLERS |

| GMS81C5108-UDXXX | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:MICROCONTROLLER|8-BIT|CMOS|QFP|80PIN|PLASTIC |

| GMS81C7008 | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:HYNIX SEMICONDUCTOR INC. 8-BIT SINGLE-CHIP MICROCONTROLLERS |

發(fā)布緊急采購,3分鐘左右您將得到回復。