- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370366 > GMS81C5016-XXXQT MICROCONTROLLER|8-BIT|CMOS|QFP|44PIN|PLASTIC PDF資料下載

參數(shù)資料

| 型號: | GMS81C5016-XXXQT |

| 英文描述: | MICROCONTROLLER|8-BIT|CMOS|QFP|44PIN|PLASTIC |

| 中文描述: | 單片機| 8位|的CMOS | QFP封裝| 44PIN |塑料 |

| 文件頁數(shù): | 61/93頁 |

| 文件大?。?/td> | 853K |

| 代理商: | GMS81C5016-XXXQT |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁當(dāng)前第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁

GMS81C1404/GMS81C1408

June. 2001 Ver 1.2

59

17.1 Interrupt Sequence

An interrupt request is held until the interrupt is accepted

or the interrupt latch is cleared to “0” by a reset or an in-

struction. Interrupt acceptance sequence requires 8 f

OSC

(2

μ

s at f

XIN

=4MHz) after the completion of the current in-

struction execution. The interrupt service task is terminat-

ed upon execution of an interrupt return instruction

[RETI].

Interrupt acceptance

1. The interrupt master enable flag (I-flag) is cleared to

“0” to temporarily disable the acceptance of any follow-

ing maskable interrupts. When a non-maskable inter-

rupt is accepted, the acceptance of any following

interrupts is temporarily disabled.

2. Interrupt request flag for the interrupt source accepted is

cleared to “0”.

3. The contents of the program counter (return address)

and the program status word are saved (pushed) onto the

stack area. The stack pointer decreases 3 times.

4. The entry address of the interrupt service program is

read from the vector table address and the entry address

is loaded to the program counter.

5. The instruction stored at the entry address of the inter-

rupt service program is executed.

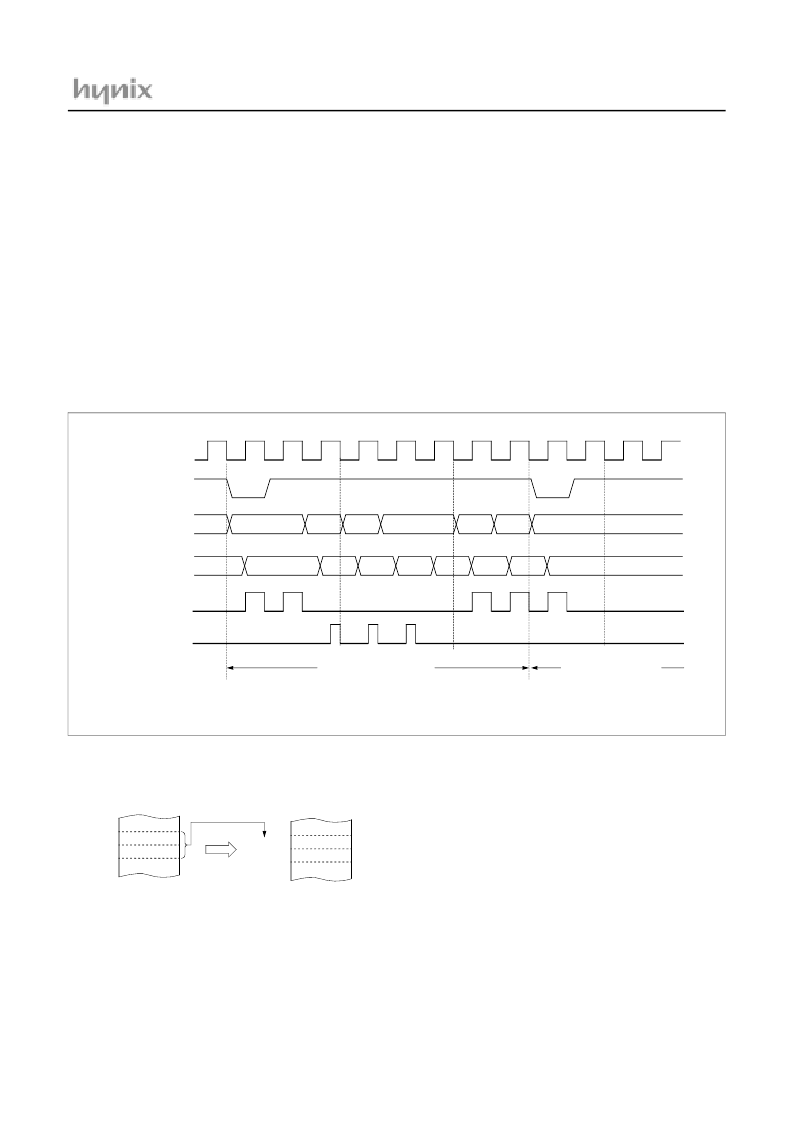

Figure 17-3 Timing chart of Interrupt Acceptance and Interrupt Return Instruction

A interrupt request is not accepted until the I-flag is set to

“1” even if a requested interrupt has higher priority than

that of the current interrupt being serviced.

When nested interrupt service is required, the I-flag should

be set to “1” by “EI” instruction in the interrupt service

program. In this case, acceptable interrupt sources are se-

lectively enabled by the individual interrupt enable flags.

Saving/Restoring General-purpose Register

During interrupt acceptance processing, the program

counter and the program status word are automatically

saved on the stack, but accumulator and other registers are

not saved itself. These registers are saved by the software

if necessary. Also, when multiple interrupt services are

nested, it is necessary to avoid using the same data memory

area for saving registers.

V.L.

System clock

Address Bus

PC

SP

SP-1

SP-2

V.H.

New PC

V.L.

Data Bus

Not used

PCH

PCL

PSW

ADL

OP code

ADH

Instruction Fetch

Internal Read

Internal Write

Interrupt Processing Step

Interrupt Service Task

V.L. and V.H. are vector addresses.

ADL and ADH are start addresses of interrupt service routine as vector contents.

Basic Interval Timer

Vector Table Address

012

H

0E3

H

0FFE6

H

0FFE7

H

0E

H

2E

H

0E312

H

0E313

H

Entry Address

Correspondence between vector table address for BIT interrupt

and the entry address of the interrupt service program.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GMS81C5016-XXXSK | MICROCONTROLLER|8-BIT|CMOS|DIP|28PIN|PLASTIC |

| GMS81C5024-XXX | MICROCONTROLLER|8-BIT|CMOS|DIP|40PIN|PLASTIC |

| GMS81C5024-XXXD | MICROCONTROLLER|8-BIT|CMOS|SOP|28PIN|PLASTIC |

| GMS81C5024-XXXDT | MICROCONTROLLER|8-BIT|CMOS|SOP|28PIN|PLASTIC |

| GMS81C5024-XXXPL | MICROCONTROLLER|8-BIT|CMOS|LDCC|44PIN|PLASTIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| GMS81C5016-XXXSK | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MICROCONTROLLER|8-BIT|CMOS|DIP|28PIN|PLASTIC |

| GMS81C5024 | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:8-BIT SINGLE CHIP MICROCONTROLLERS |

| GMS81C5024-XXX | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MICROCONTROLLER|8-BIT|CMOS|DIP|40PIN|PLASTIC |

| GMS81C5024-XXXD | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MICROCONTROLLER|8-BIT|CMOS|SOP|28PIN|PLASTIC |

| GMS81C5024-XXXDT | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MICROCONTROLLER|8-BIT|CMOS|SOP|28PIN|PLASTIC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。