- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67592 > FS6131-01G (ON SEMICONDUCTOR) PLL FREQUENCY SYNTHESIZER, 27 MHz, PDSO16 PDF資料下載

參數(shù)資料

| 型號: | FS6131-01G |

| 廠商: | ON SEMICONDUCTOR |

| 元件分類: | PLL合成/DDS/VCOs |

| 英文描述: | PLL FREQUENCY SYNTHESIZER, 27 MHz, PDSO16 |

| 封裝: | 0.150 INCH, GREEN, SOP-16 |

| 文件頁數(shù): | 37/40頁 |

| 文件大小: | 746K |

| 代理商: | FS6131-01G |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁當(dāng)前第37頁第38頁第39頁第40頁

For applications where an external loop filter is required, the following analysis example can be used to determine loop gain and stability.

The loop gain of a PLL is the product of all of the gains within the loop.

Establish the basic operating parameters:

6

AMI Semiconductor - Rev. 2.0, Jun. 05

www.amis.com

FS6131-01/FS6131-01g Programmable Line Lock Clock Generator IC

Data Sheet

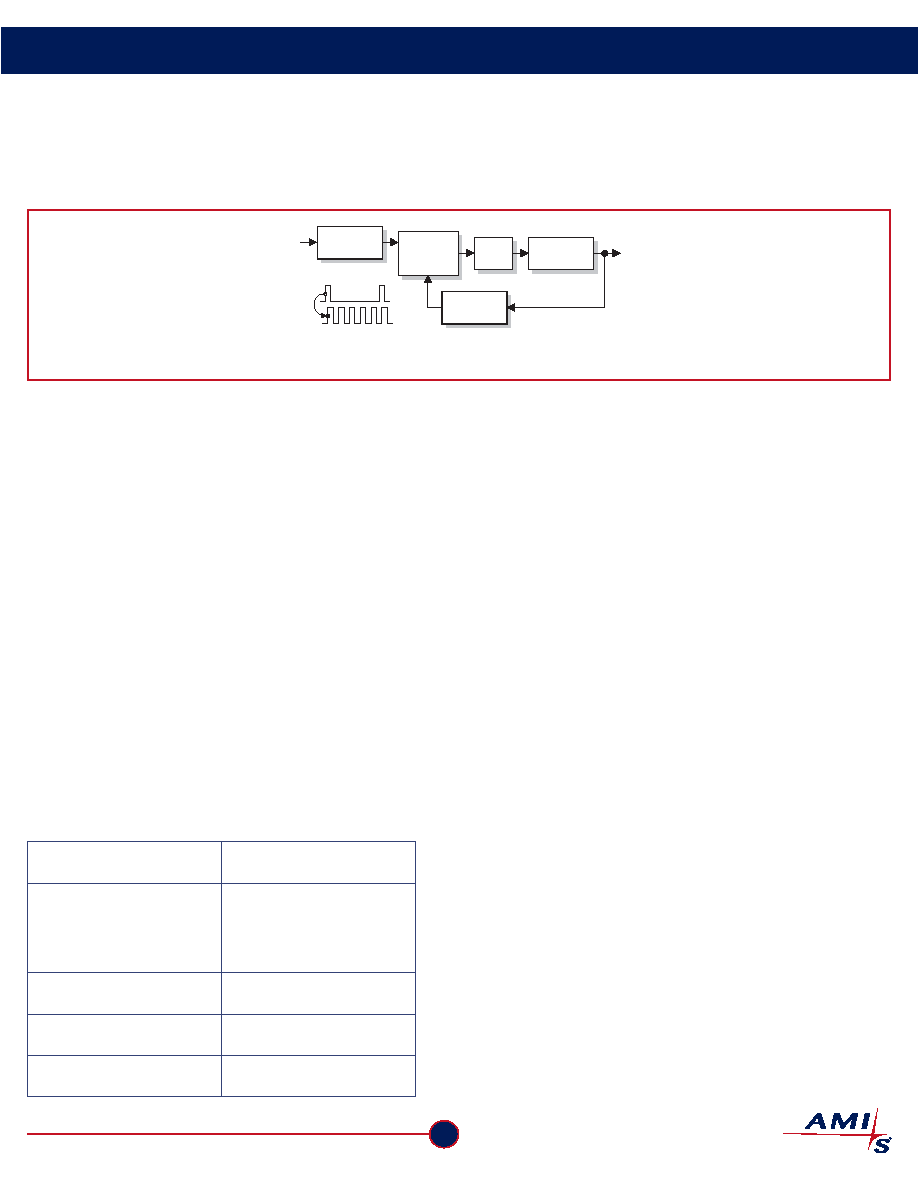

4.2.2 Phase Alignment

To maintain a fixed phase relation between input and output clocks, the post divider must be placed inside the feedback loop. The source for the

feedback divider is obtained from the output of the post divider via the FBKDSRC switch. In addition, the feedback divider must be dividing at a

multiple of the post divider.

Phase

Frequency

Detect

Feedback

Divider (N

F)

VCO

f

IN

f

OUT

Reference

Divider (N

R)

Post

Divider (N

F)

f

IN

f

OUT

Figure 7: Aligned I/O Phase

4.2.3 Phase Sampling and Initial Alignment

However, the ability to adjust the phase is useless without knowing the initial relation between output and input phase. To aid in the initial

synchronization of the output phase to input phase, a phase align "flag" makes a transition (zero to one or one to zero) when the output clock

phase becomes aligned with the feedback source phase. The feedback source clock is, by definition, locked to the input clock phase.

First, the FS6131 is used to sample the output clock with the feedback source clock and set/clear the phase align flag when the two clocks match

to within a feedback source clock period. Then, the clock gobbler is used to delay the output phase relative to the input phase one VCO clock at

a time until a transition on the flag occurs. When a transition occurs, the output and input clocks are phase aligned.

To enter this mode, set STAT[1] to one and clear STAT[0] to zero. If the CMOS bit is set to one, the LOCK/IPRG pin can display the flag. The flag

is always available under software control by reading back the STAT[1] bit, which will be overwritten by the flag in this mode.

4.2.4 Feedback Divider Monitoring

The feedback divider clock can be brought out the LOCK/IPRG pin independent of the output clock to allow monitoring of the feedback divider

clock. To enter this mode, set both the STAT[1] and STAT[0] bits to one. The CMOS bit must also be set to one to enable the LOCK/IPRG pin as

an output.

4.3 Loop Gain Analysis

Set the charge pump current:

Set the loop filter values:

Set the VCO gain (VCOSPD):

Set the feedback divider:

Set the reference frequency (at

the input to the phase detector):

A

I

chgpump

m

10

=

pF

C

F

C

k

R

LF

220

015

.

0

15

2

1

=

W

=

m

kHz

f

REF

20

=

3500

=

F

N

V

MHz

A

VCO

/

230

=

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| FS6131-01G | PLL FREQUENCY SYNTHESIZER, 27 MHz, PDSO16 |

| FS6131-01 | PLL FREQUENCY SYNTHESIZER, 27 MHz, PDSO16 |

| FS6131-01 | PLL FREQUENCY SYNTHESIZER, 27 MHz, PDSO16 |

| FS6S0965R-YDTU | 36 A SWITCHING REGULATOR, 150 kHz SWITCHING FREQ-MAX, PZFM5 |

| FS6S0965R-TU | 36 A SWITCHING REGULATOR, 150 kHz SWITCHING FREQ-MAX, PSFM5 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| FS6131-01G-XTD | 功能描述:時(shí)鐘發(fā)生器及支持產(chǎn)品 I2C PROG PLL CLK RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

| FS6131-01G-XTP | 功能描述:時(shí)鐘發(fā)生器及支持產(chǎn)品 I2C PROG PLL CLK RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

| FS6131-01I-XTD | 功能描述:時(shí)鐘發(fā)生器及支持產(chǎn)品 I2C PROG PLL CLK (IND) RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

| FS6131-01I-XTP | 功能描述:時(shí)鐘發(fā)生器及支持產(chǎn)品 I2C PROG PLL CLK IND RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

| FS6186-16/24 | 制造商:Schaffner 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。