- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67592 > FS6131-01 (ON SEMICONDUCTOR) PLL FREQUENCY SYNTHESIZER, 27 MHz, PDSO16 PDF資料下載

參數(shù)資料

| 型號(hào): | FS6131-01 |

| 廠商: | ON SEMICONDUCTOR |

| 元件分類: | PLL合成/DDS/VCOs |

| 英文描述: | PLL FREQUENCY SYNTHESIZER, 27 MHz, PDSO16 |

| 封裝: | 0.150 INCH, SOP-16 |

| 文件頁(yè)數(shù): | 22/40頁(yè) |

| 文件大?。?/td> | 746K |

| 代理商: | FS6131-01 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)當(dāng)前第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)

29

AMI Semiconductor - Rev. 2.0, Jun. 05

www.amis.com

FS6131-01/FS6131-01g Programmable Line Lock Clock Generator IC

Data Sheet

Table 21: Sample Text Output

AMI - FS6131 Solution Text File

Line-Locked / Genlock Mode

Desired Multiple =

800

Source =

.0315MHz Reference Pin

External Loop Filter C1 = 47pF

R = 4700Ohms

Crystal Oscillator Voltage Tune Disabled

Output Stage = CMOS

Reference Divider

=

1

Feedback Divider

=

800

Post Divider

=

4

Charge Pump (uA)

=

0

EXTLF

=

1

XLVTEN

=

0

XCT

=

7

CMOS

=

1

Register 0

= 1H (1)

Register 1

= 40H (64)

Register 2

= 2H (2)

Register 3

= 20H (32)

Register 4

= 3H (3)

Register 5

= 24H (36)

Register 6

= 0H (0)

Register 7

= 17H (23)

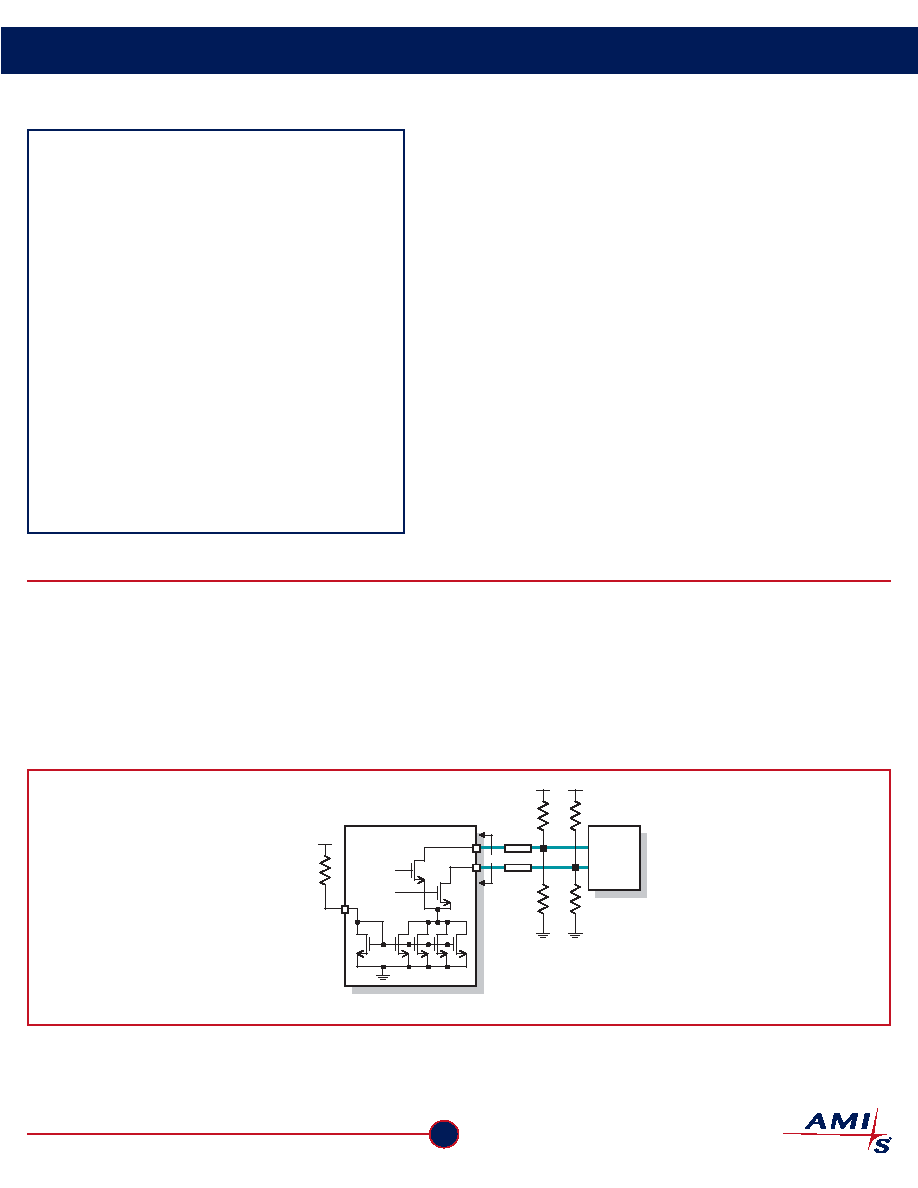

11.0 Applications Information

11.1 PECL Output Mode

A signal reflection will occur at any point on a PC-board trace where impedance mismatches exist. Reflections cause several undesirable effects

in high-speed applications, such as an increase in clock jitter and a rise in electromagnetic emissions from the board. Using a properly designed

series termination on each high-speed line can alleviate these problems by eliminating signal reflections.

If a PECL interface is desired, the transmission line must be terminated using a Thévenin, or dual, termination. The output stage can only sink

current in the PECL mode, and the amount of sink current is set by a programming resistor on the LOCK/IPRG pin. Source current is provided by

the pull-up resistor that is part of the Thévenin termination.

R

p1

IPRG

CLKN

CLKP

{

from

PLL

R

n1

R

p2

R

n2

R

i

LOAD

z

L

z

L

z

O

PECL Mode Output

V

CC

V

CC

Figure 22: Thévenin termination (PECL)

Thévenin termination uses two resistors per transmission line. The parallel resistance of the termination resistors should be sized to equal the

transmission line impedance, taking into account the driver sink current, the desired rise and fall times, and the VIH and VIL specifications of the

load.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| FS6S0965R-YDTU | 36 A SWITCHING REGULATOR, 150 kHz SWITCHING FREQ-MAX, PZFM5 |

| FS6S0965R-TU | 36 A SWITCHING REGULATOR, 150 kHz SWITCHING FREQ-MAX, PSFM5 |

| FS6S1265RE-YDTU | 48 A SWITCHING REGULATOR, 150 kHz SWITCHING FREQ-MAX, PZFM5 |

| FS6S1265RB-YDTU | 48 A SWITCHING REGULATOR, 150 kHz SWITCHING FREQ-MAX, PZFM5 |

| FS6S0965RT-YDTU | 36 A SWITCHING REGULATOR, 150 kHz SWITCHING FREQ-MAX, PZFM5 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| FS6131-01G | 制造商:ONSEMI 制造商全稱:ON Semiconductor 功能描述:Programmable Line Lock Clock Generator IC |

| FS6131-01G-XTD | 功能描述:時(shí)鐘發(fā)生器及支持產(chǎn)品 I2C PROG PLL CLK RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

| FS6131-01G-XTP | 功能描述:時(shí)鐘發(fā)生器及支持產(chǎn)品 I2C PROG PLL CLK RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

| FS6131-01I-XTD | 功能描述:時(shí)鐘發(fā)生器及支持產(chǎn)品 I2C PROG PLL CLK (IND) RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

| FS6131-01I-XTP | 功能描述:時(shí)鐘發(fā)生器及支持產(chǎn)品 I2C PROG PLL CLK IND RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。