- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67504 > FM33256-GTR SPECIALTY CONSUMER CIRCUIT, PDSO14 PDF資料下載

參數(shù)資料

| 型號: | FM33256-GTR |

| 元件分類: | 消費家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PDSO14 |

| 封裝: | GREEN, MO-012AB, SOIC-14 |

| 文件頁數(shù): | 17/28頁 |

| 文件大小: | 320K |

| 代理商: | FM33256-GTR |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁當前第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁

FM33256/FM3316 SPI Companion w/ FRAM

Rev. 2.0

Feb. 2009

Page 24 of 28

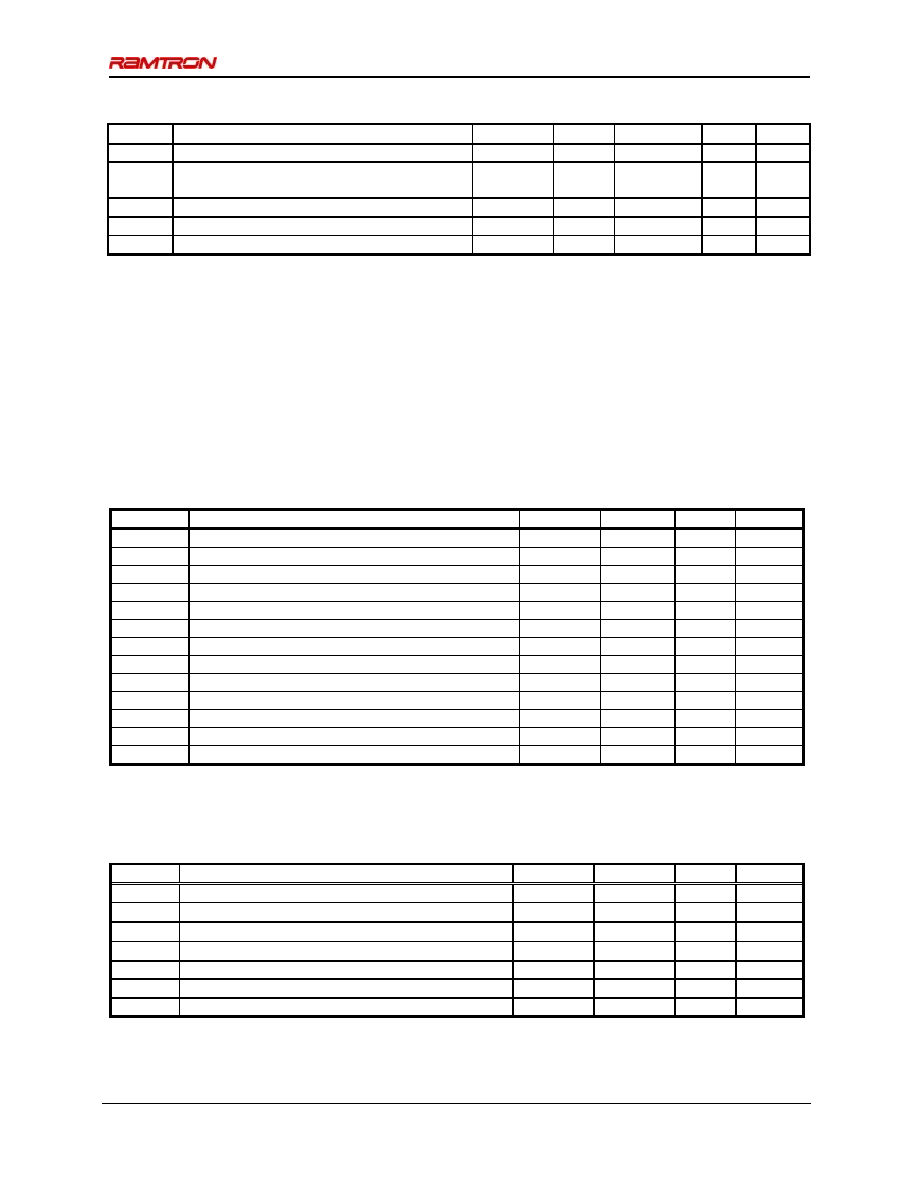

DC Operating Conditions, continued (TA = -40° C to + 85° C, VDD = 2.7V to 3.6V unless otherwise specified)

Symbol

Parameter

Min

Typ

Max

Units

Notes

VOL

Output Low Voltage @ IOL = 3 mA

-

0.4

V

VOH

Output High Voltage

(SO, PFO) @ IOH = -2 mA

VDD – 0.8

-

V

RRST

Pull-up resistance for /RST inactive

50

400

K

VPFI

Power Fail Input Reference Voltage

1.475

1.50

1.525

V

VHYS

Power Fail Input (PFI) Hysteresis (Rising)

-

100

mV

Notes

1.

Full complete operation. Supervisory circuits, RTC, etc operate to lower voltages as specified.

2.

SCK toggling between VDD-0.3V and VSS, other inputs VSS or VDD-0.3V.

3.

All inputs at VSS or VDD, static. Trickle charger off (VBC=0).

4.

The VBAK trickle charger automatically regulates the maximum voltage on this pin for capacitor backup applications.

5.

VBAK = 3.0V, VDD < VSW, oscillator running, CNT at VBAK.

6.

VBAK will source current when trickle charge is enabled (VBC bit=1), VDD > VBAK, and VBAK < VBAK max.

7.

This is the VDD supply current contributed by enabling the trickle charger circuit, and does not account for IBAKTC.

8.

This is the VDD supply current contributed by enabling the watchdog circuit, WDE=1 and WDET set to a non-zero value.

9.

/RST is asserted active when VDD < VTP .

10. The minimum VDD to guarantee the level of /RST remains a valid VOL level.

11. VIN or VOUT = VSS to VDD. Does not apply to PFI, X1, or X2.

12. Includes /RST input detection of external reset condition to trigger driving of /RST signal by FM33xx.

AC Parameters (TA = -40°C to + 85°C, VDD = 2.7V to 3.6V CL = 30 pF)

Symbol

Parameter

Min

Max

Units

Notes

fCK

SCK Clock Frequency

0

16

MHz

tCH

Clock High Time

28

ns

1

tCL

Clock Low Time

28

ns

1

tCSU

Chip Select Setup

10

ns

tCSH

Chip Select Hold

10

ns

tOD

Output Disable Time

20

ns

2

tODV

Output Data Valid Time

24

ns

tOH

Output Hold Time

0

ns

tD

Deselect Time

90

ns

tR

Data In Rise Time

50

ns

1,3

tF

Data In Fall Time

50

ns

1,3

tSU

Data Setup Time

6

ns

tH

Data Hold Time

6

ns

Notes

1.

tCH + tCL = 1/fCK.

2.

This parameter is characterized but not 100% tested.

3.

Rise and fall times measured between 10% and 90% of waveform.

Supervisor Timing (TA = -40° C to + 85° C, VDD = 2.7V to 3.6V)

Symbol

Parameter

Min

Max

Units

Notes

tRPW

/RST Pulse Width (active low time)

30

100

ms

tRNR

/RST Response Time to VDD<VTP (noise filter)

7

25

s

1

tVR

VDD Rise Time

50

-

s/V

1,2

tVF

VDD Fall Time

100

-

s/V

1,2

tWDST

Watchdog StartTime

0.3*tDOG1

tDOG1

ms

3

tWDET

Watchdog EndTime

tDOG2

3.3*tDOG2

ms

3

fCNT

Frequency of Event Counter

0

1

kHz

Notes

1

This parameter is characterized but not tested.

2

Slope measured at any point on VDD waveform.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| FM33256-G | SPECIALTY CONSUMER CIRCUIT, PDSO14 |

| FM4005-G | SPECIALTY CONSUMER CIRCUIT, PDSO14 |

| FME270-461/ES | 1 FUNCTIONS, 400 V, 1.5 A, DATA LINE FILTER |

| FME270-461V/ES | 1 FUNCTIONS, 400 V, 1.5 A, DATA LINE FILTER |

| FME270-461W/ES | 1 FUNCTIONS, 400 V, 1.5 A, DATA LINE FILTER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| FM333 | 制造商:Black Box Corporation 功能描述:ST ADAPTER SNAP FITTING |

| FM334C | 制造商:Black Box Corporation 功能描述:GigaPlus Blank Wallplate Insert, Ivory, 20-Pack |

| FM335 | 制造商:Black Box Corporation 功能描述:BLANK SNAP FITTING 10 PAK ELECTRICAL IVORY |

| FM336 | 制造商:Black Box Corporation 功能描述:GigaStation Blank Snap Fitting, Gray, 10-Pack |

| FM336PLUS | 制造商:CONEXANT 制造商全稱:CONEXANT 功能描述:V.34/Group 3 High Performance Fax Modem Family |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。