- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370155 > FBL2031 (NXP Semiconductors N.V.) 9-bit BTL 3.3V latched/registered/pass-thru Futurebus transceiver PDF資料下載

參數(shù)資料

| 型號: | FBL2031 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | 9-bit BTL 3.3V latched/registered/pass-thru Futurebus transceiver |

| 中文描述: | 9位橋接3.3鎖存/注冊/直通Futurebus收發(fā)器 |

| 文件頁數(shù): | 10/16頁 |

| 文件大小: | 165K |

| 代理商: | FBL2031 |

Philips Semiconductors

Product specification

FBL2031

9-bit BTL 3.3V latched/registered/pass-thru

Futurebus+ transceiver

2000 Apr 18

10

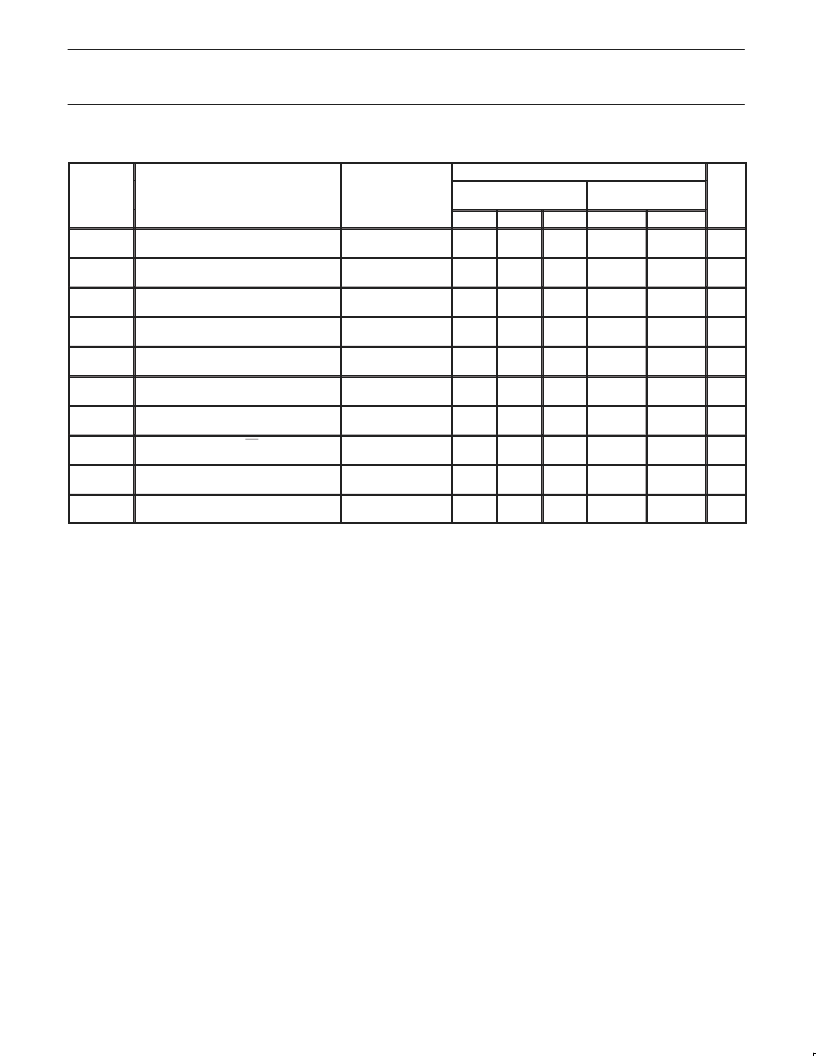

AC ELECTRICAL CHARACTERISTICS

A TO B 9

LOAD SPECIFICATIONS

T

amb

= +25

°

C,

CC

= 3.3V,

MIN

TYP

MAX

SYMBOL

PARAMETER

TEST

CONDITION

T

amb

= –40 to +85

°

C,

CC

= 3.3V

±

10%,

MIN

UNIT

MAX

t

PLH

t

PHL

t

PLH

t

PHL

t

PLH

t

PHL

t

PLH

t

PHL

t

PLH

t

PHL

t

PLH

t

PHL

t

PLH

t

PHL

t

TLH

t

THL

Propagation delay (thru latch)

An to Bn

Propagation delay (transparent latch)

An to Bn

Propagation delay

LCAB to Bn (latch)

Propagation delay

LCAB to Bn (register)

Propagation delay

SEL0 or SEL1 to Bn (inverting)

Propagation delay

SEL0 or SEL1 to Bn (non-inverting)

Waveform 1, 2

1.4

1.3

1.7

2.0

8.8

8.4

2.3

2.5

2.3

1.3

2.0

2.6

1.2

1.9

2.6

2.5

2.9

3.5

11.6

11.0

3.6

4.0

3.8

4.8

4.4

4.3

2.9

3.3

3.8

3.8

4.2

5.0

14.5

13.7

5.0

5.4

5.5

8.8

7.2

6.1

4.8

4.7

1.0

1.0

1.0

1.5

6.7

6.7

1.4

1.9

1.2

1.0

1.1

1.7

1.0

1.2

1.2

0.4

4.9

4.2

5.4

5.7

17.9

16.6

6.2

6.4

7.0

9.6

8.5

7.6

5.8

6.4

3.0

1.5

ns

Waveform 1, 2

ns

Waveform 1, 2

ns

Waveform 1, 2

ns

Waveform 1, 2

ns

Waveform 1, 2

ns

OEBn to Bn

Waveform 1, 2

ns

Output transition time, Bn Port

(1.3V to 1.8V)

Output to output skew for multiple

channels

1

Pulse skew

2

t

PHL

– t

PLH

MAX

Test Circuit and

Waveforms

ns

t

SK

(o)

Waveform 3

0.4

1.0

2.0

ns

t

SK

(p)

Waveform 2

0.3

1.0

1.5

ns

NOTES:

1.

t

actual – t

actual

for any data input to output path compared to any other data input to output path where N and M are either LH or

HL. Skew times are valid only under same test conditions (temperature, V

CC

, loading, etc.). t

SK

(0) compares t

PLH

on a given path to t

PLH

on any other path or compares t

PHL

on a given path to t

PHL

on any other path.

2. t

SK

(p) is used to quantify duty cycle characteristics. In essence it compares the input signal duty cycle to the corresponding output signal

duty cycle (50MHz input frequency and 50% duty cycle, tested on data paths only).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| FBL2031BB | 9-bit BTL 3.3V latched/registered/pass-thru Futurebus transceiver |

| FBL2033 | 3.3V BTL 8-bit latched/registered/pass-thru universal transceiver |

| FBL2033BB | 3.3V BTL 8-bit latched/registered/pass-thru universal transceiver |

| FBL2040 | 3.3V BTL8-bit TTL to BTL transceiver |

| FBL2040BB | 3.3V BTL8-bit TTL to BTL transceiver |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| FBL2031BB | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:9-bit BTL 3.3V latched/registered/pass-thru Futurebus transceiver |

| FBL2031BB-T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:9-Bit Bus Transceiver |

| FBL2033 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:3.3V BTL 8-bit latched/registered/pass-thru universal transceiver |

| FBL2033BB | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:3.3V BTL 8-bit latched/registered/pass-thru Futurebus universal interface transceiver |

| FBL2040 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:3.3V BTL8-bit TTL to BTL transceiver |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。