- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370152 > FB2033BB (NXP SEMICONDUCTORS) 8-bit latched/registered/pass-thru Futurebus universal interface transceiver PDF資料下載

參數(shù)資料

| 型號: | FB2033BB |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 通用總線功能 |

| 英文描述: | 8-bit latched/registered/pass-thru Futurebus universal interface transceiver |

| 中文描述: | TTL/H/L SERIES, 8-BIT REGISTERED TRANSCEIVER, INVERTED OUTPUT, PQFP52 |

| 封裝: | PLASTIC, QFP-52 |

| 文件頁數(shù): | 8/10頁 |

| 文件大小: | 173K |

| 代理商: | FB2033BB |

Philips Semiconductors

Product specification

FB2033

8-bit latched/registered/pass-thru

Futurebus+ universal interface transceiver

1995 May 25

8

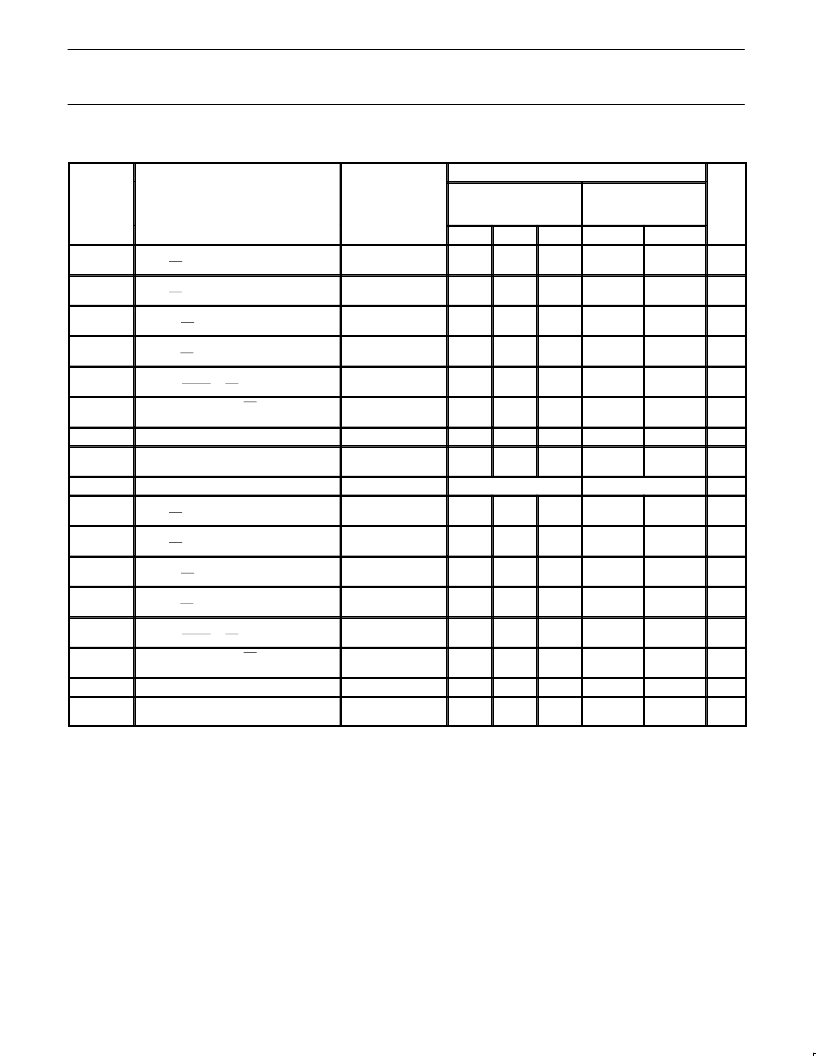

AC ELECTRICAL CHARACTERISTICS

(Continued)

SYMBOL

PARAMETER

TEST

CONDITION

B PORT LIMITS

UNIT

T

amb

= +25

°

C, V

CC

= 5V,

D

= 30pF, R

U

T

amb

= 0 to 70

°

C,

V

= 5V

±

10%,

C

D

= 30pF, R

U

= 9

MIN

TYP

MAX

MIN

MAX

t

PLH

t

PHL

t

PLH

t

PHL

t

PLH

t

PHL

t

PLH

t

PHL

t

PZH

t

PZL

Propagation delay (thru mode)

AIn to Bn

Waveform 1, 2

1.2

1.0

2.9

2.9

4.3

4.4

1.0

1.0

4.8

4.6

ns

Propagation delay (transparent latch)

AIn to Bn

Waveform 1, 2

1.4

1.0

3.1

3.3

4.5

4.8

1.0

1.0

5.1

5.1

ns

Propagation delay

LCAB to Bn

Waveform 1, 2

2.7

2.2

4.4

5.1

5.7

6.6

2.4

2.0

6.4

7.1

ns

Propagation delay

SABn to Bn

Waveform 1, 2

1.8

1.0

3.6

3.3

5.0

4.9

1.4

1.0

5.7

5.2

ns

Enable/disable time

OEB0 or OEB1 to Bn

Waveform 1, 2

1.4

1.0

3.0

3.1

4.5

5.0

1.0

1.0

5.0

5.6

ns

V/

t

Output transition rate, Bn Port

20% to 80%, 80% to 20%

Output to output skew, B port

1

Test Circuit and

Waveforms

0.4

1.2

V/ns

t

SK

(o)

Waveform 3

0.8

1.5

2.0

ns

t

SK

(p)

Pulse skew 2

t

PHL

– t

PLH

MAX

Waveform 2

0.3

1.5

ns

SYMBOL

PARAMETER

TEST CONDITION

R

U

= 16.5

3.0

3.0

R

U

= 16.5

1.0

1.0

UNIT

t

PLH

t

PHL

t

PLH

t

PHL

t

PLH

t

PHL

t

PLH

t

PHL

t

PZH

t

PZL

Propagation delay (thru mode)

AIn to Bn

Waveform 1, 2

1.2

1.0

4.4

4.5

4.9

4.7

ns

Propagation delay (transparent latch)

AIn to Bn

Waveform 1, 2

1.4

1.0

3.2

3.4

4.6

4.9

1.0

1.0

5.2

5.2

ns

Propagation delay

LCAB to Bn

Waveform 1, 2

2.7

2.2

4.5

5.2

5.8

6.7

2.4

2.0

6.5

7.2

ns

Propagation delay

SABn to Bn

Waveform 1, 2

1.8

1.0

3.7

3.4

5.1

5.0

1.4

1.0

5.8

5.3

ns

Enable/disable time

OEB0 or OEB1 to Bn

Waveform 1, 2

1.4

1.0

3.1

3.2

4.6

5.1

1.0

1.0

5.1

5.7

ns

V/

t

Output transition rate, Bn Port

20% to 80%, 80% to 20%

Output to output skew, B port

1

Pulse skew

2

t

PHL

– t

PLH

MAX

Test Circuit and

Waveforms

0.2

0.6

V/ns

t

SK

(o)

Waveform 3

0.5

1.0

1.5

ns

t

SK

(p)

Waveform 2

0.3

1.0

1.5

ns

NOTES:

1.

t

PN

actual – t

PM

actual

for any data input to output path compared to any other data input to output path where N and M are either LH or

HL. Skew times are valid only under same test conditions (temperature, V

CC

, loading, etc.).

2. t

SK

(p) is used to quantify duty cycle characteristics. In essence it compares the input signal duty cycle to the corresponding output signal

duty cycle (50MHz input frequency and 50% duty cycle, tested on data paths only).

相關PDF資料 |

PDF描述 |

|---|---|

| FB2040A | 8-bit Futurebus transceiver |

| FB2040BB | 8-bit Futurebus transceiver |

| FB2041BB-T | 7-Bit Bus Transceiver |

| FB2041 | 7-bit Futurebus+ transceiver(7位預置總線收發(fā)器) |

| FB2041BB | 7-bit Futurebus transceiver |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| FB2033BB-T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Single 8-Bit Inverting Bus Transceiver |

| FB2033K | 制造商:TI 制造商全稱:Texas Instruments 功能描述:8-BIT TTL/BTL REGISTERED TRANSCEIVER |

| FB-20-4 | 制造商:Polycase 功能描述:Enclosure |

| FB2040 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:8-BIT TTL/BTL TRANSCEIVER |

| FB20401 | 制造商:Marathon Special Products 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。