- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄299033 > EPM3256AQC208-6 (ALTERA CORP) EE PLD, 6 ns, PQFP208 PDF資料下載

參數(shù)資料

| 型號: | EPM3256AQC208-6 |

| 廠商: | ALTERA CORP |

| 元件分類: | PLD |

| 英文描述: | EE PLD, 6 ns, PQFP208 |

| 封裝: | PLASTIC, QFP-208 |

| 文件頁數(shù): | 9/43頁 |

| 文件大小: | 716K |

| 代理商: | EPM3256AQC208-6 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁當前第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁

Altera Corporation

17

MAX 3000A Programmable Logic Device Family Data Sheet

Preliminary Information

The VCCIO pins can be connected to either a 3.3-V or 2.5-V power supply,

depending on the output requirements. When the VCCIO pins are

connected to a 2.5-V power supply, the output levels are compatible with

2.5-V systems. When the VCCIO pins are connected to a 3.3-V power

supply, the output high is at 3.3 V and is therefore compatible with 3.3-V

or 5.0-V systems. Devices operating with VCCIO levels lower than 3.0 V

incur a nominally greater timing delay of tOD2 instead of tOD1. Inputs can

always be driven by 2.5-V, 3.3-V, or 5.0-V signals.

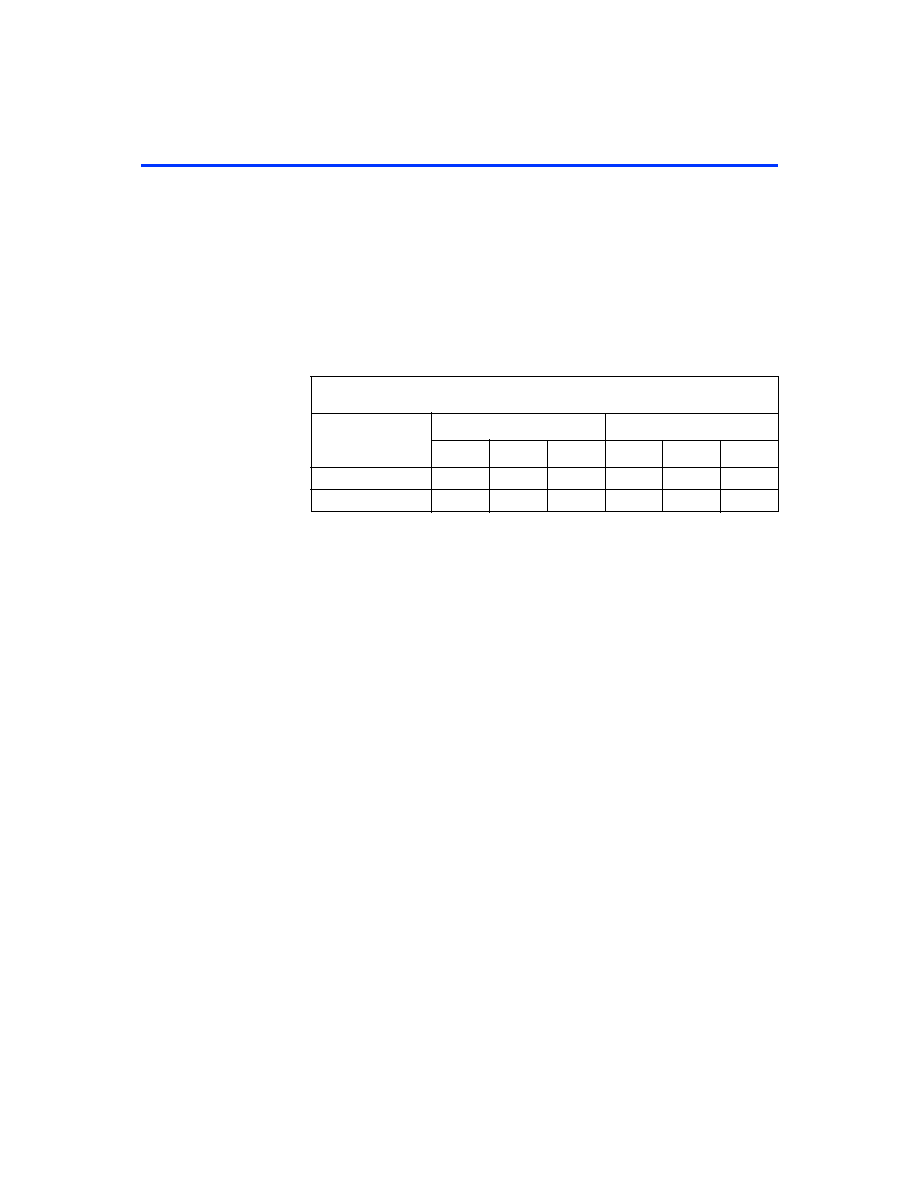

Table 8 summarizes the MAX 3000A MultiVolt I/O support.

Note:

(1)

When VCCIO is 3.3 V, a MAX 3000A device can drive a 2.5-V device that has 3.3-V

tolerant inputs.

Open-Drain Output Option

MAX 3000A devices provide an optional open-drain (equivalent to

open-collector) output for each I/O pin. This open-drain output enables

the device to provide system-level control signals (e.g., interrupt and

write enable signals) that can be asserted by any of several devices. It can

also provide an additional wired-OR plane.

Slew-Rate Control

The output buffer for each MAX 3000A I/O pin has an adjustable output

slew rate that can be configured for low-noise or high-speed performance.

A faster slew rate provides high-speed transitions for high-performance

systems. However, these fast transitions may introduce noise transients

into the system. A slow slew rate reduces system noise, but adds a

nominal delay of 4 to 5 ns. When the configuration cell is turned off, the

slew rate is set for low-noise performance. Each I/O pin has an individual

EEPROM bit that controls the slew rate, allowing designers to specify the

slew rate on a pin-by-pin basis. The slew rate control affects both the

rising and falling edges of the output signal.

Table 8. MAX 3000A MultiVolt I/O Support

VCCIO Voltage

Input Signal (V)

Output Signal (V)

2.5

3.3

5.0

2.5

3.3

5.0

2.5

v

3.3

v

v (1)

v

相關PDF資料 |

PDF描述 |

|---|---|

| EPM3256AQI208-6 | EE PLD, 6 ns, PQFP208 |

| EPM7128ABC100-6 | EE PLD, 6 ns, PBGA100 |

| EPM7128ABC100-7 | EE PLD, 7.5 ns, PBGA100 |

| EPM7128ABI100-10 | EE PLD, 10 ns, PBGA100 |

| EPM7128ABI100-12 | EE PLD, 12 ns, PBGA100 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| EPM3256AQC208-7 | 功能描述:CPLD - 復雜可編程邏輯器件 CPLD - MAX 3000A 256 Macro 161 IOs RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| EPM3256AQC208-7N | 功能描述:CPLD - 復雜可編程邏輯器件 CPLD - MAX 3000A 256 Macro 161 IOs RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| EPM3256AQI208-10 | 功能描述:CPLD - 復雜可編程邏輯器件 CPLD - MAX 3000A 256 Macro 161 IOs RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| EPM3256AQI208-10N | 功能描述:CPLD - 復雜可編程邏輯器件 CPLD - MAX 3000A 256 Macro 161 IOs RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| EPM3256ATC100-5N | 制造商:ALTERA 制造商全稱:Altera Corporation 功能描述:Higha??performance, lowa??cost CMOS EEPROMa??based programmable |

發(fā)布緊急采購,3分鐘左右您將得到回復。