- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄362743 > EP9315-CB (CIRRUS LOGIC INC) Enhanced Universal Platform System-on-Chip Processor PDF資料下載

參數(shù)資料

| 型號(hào): | EP9315-CB |

| 廠(chǎng)商: | CIRRUS LOGIC INC |

| 元件分類(lèi): | 微控制器/微處理器 |

| 英文描述: | Enhanced Universal Platform System-on-Chip Processor |

| 中文描述: | 32-BIT, 200 MHz, RISC PROCESSOR, PBGA352 |

| 封裝: | 27 X 27 MM, PLASTIC, MO-151BAL-2, BGA-352 |

| 文件頁(yè)數(shù): | 34/64頁(yè) |

| 文件大小: | 1031K |

| 代理商: | EP9315-CB |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)當(dāng)前第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)

34

Copyright 2005 Cirrus Logic (All Rights Reserved)

DS638PP4

EP9315

Enhanced Universal Platform SOC Processor

PIO Data Transfers

Note:

1. t

0

is the minimum total cycle time, t

2

is the minimum DIORn / DIOWn assertion time, and t

2i

is the minimum DIORn / DIOWn

negation time. A host implementation shall lengthen t

2

and/or t

2i

to ensure that t

0

is equal to or greater than the value

reported in the devices IDENTIFY DEVICE data. A device implementation shall support any legal host implementation.

2. This parameter specifies the time from the negation edge of DIORn to the time that the data bus is released by the device.

3. The delay from the activation of DIORn or DIOWn until the state of IORDY is first sampled. If IORDY is inactive then the host

shall wait until IORDY is active before the register transfer cycle is completed. If the device is not driving IORDY negated at

the t

A

after the activation of DIORn or DIOWn, then t

5

shall be met and t

RD

is not applicable. If the device is driving IORDY

negated at the time t

A

after the activation of DIORn or DIOWn, then t

RD

shall be met and t

5

is not applicable.

4. Timings based upon software control. See User’s Guide.

5. All IDE timing is based upon HCLK = 100 MHz.

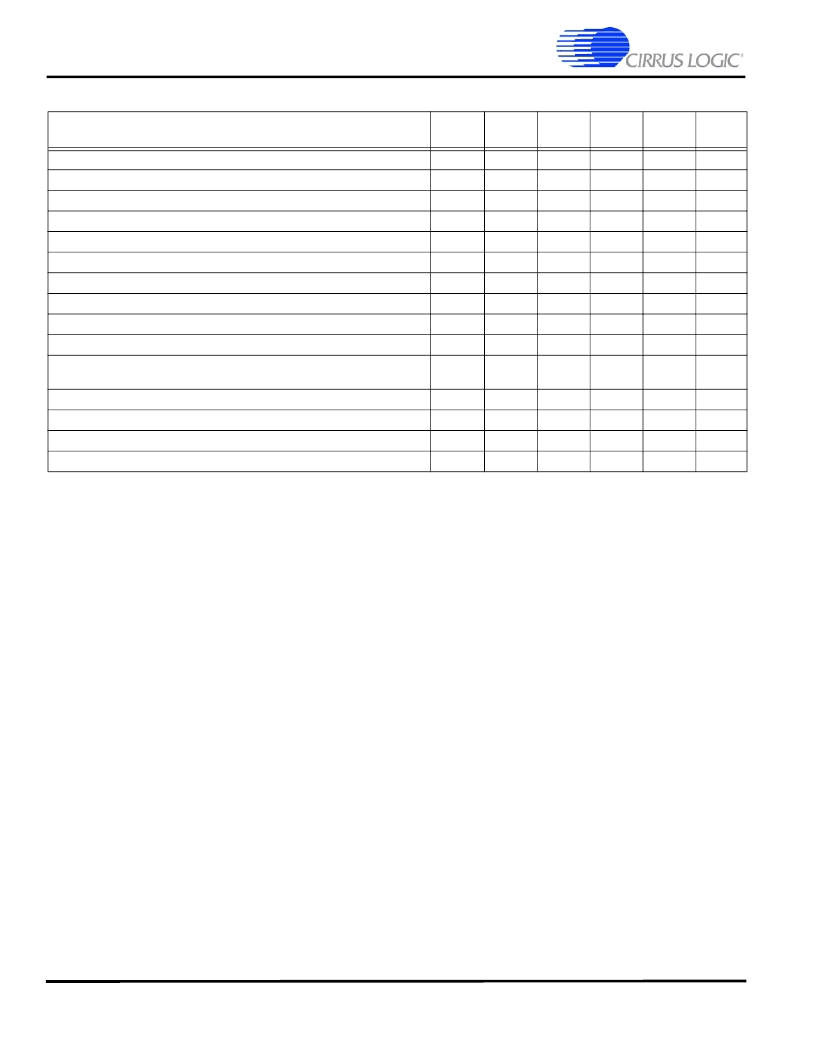

Parameter

Symbol

Mode 0

(in ns)

Mode 1

(in ns)

Mode 2

(in ns)

Mode 3

(in ns)

Mode 4

(in ns)

Cycle time

(min)

(Note 1, 4)

t

0

600

383

240

180

120

Address valid to DIORn / DIOWn setup

(min)

(Note 4)

t

1

70

50

30

30

25

DIORn / DIOWn 16-bit

(min)

(Note 1, 4)

t

2

165

125

100

80

70

DIORn / DIOWn recovery time

(min)

(Note 1, 4)

t

2i

-

-

-

70

25

DIOWn data setup

(min)

(Note 4)

t

3

60

45

30

30

20

DIOWn data hold

(min)

t

4

0

0

0

0

0

DIORn data setup

(min)

t

5

20

20

20

20

20

DIORn data hold

(min)

t

6

0

0

0

0

0

DIORn data high impedance state

(max)

(Note 2, 4)

t

6z

30

30

30

30

30

DIORn / DIOWn to address valid hold

(min)

(Note 4)

t

9

20

15

10

10

10

Read Data Valid to IORDY

active (if IORDY initially low after t

A

)

(min)

(Note 4)

t

RD

0

0

0

0

0

IORDY Setup time

(Note 3, 4)

t

A

35

35

35

35

35

IORDY Pulse Width

(max)

(Note 4)

t

B

1250

1250

1250

1250

1250

IORDY assertion to release

(max)

t

C

5

5

5

5

5

DIOWn assert to data valid

(max)

t

DDV

10

10

10

10

10

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EP9315-CBZ | Enhanced Universal Platform System-on-Chip Processor |

| EPA480C-SOT89 | DC-6GHz High Efficiency Heterojunction Power FET |

| EPA480 | DC-6GHz High Efficiency Heterojunction Power FET |

| EPB025A | Low Noise High Gain Heterojunction FET |

| EPC16 | Configuration Devices for SRAM-Based LUT Devices |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EP9315CB/E0 | 制造商:Cirrus Logic 功能描述: |

| EP9315CB/E1 | 制造商:Cirrus Logic 功能描述: |

| EP9315-CBZ | 功能描述:微處理器 - MPU IC Universl Pltform ARM9 SOC Prcessor RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線(xiàn)寬度:32 bit 最大時(shí)鐘頻率:536 MHz 程序存儲(chǔ)器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類(lèi)型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-324 |

| EP9315-EB | 制造商:CIRRUS 制造商全稱(chēng):Cirrus Logic 功能描述:Enhanced Universal Platform System-on-Chip Processor |

| EP9315-EBZ | 制造商:CIRRUS 制造商全稱(chēng):Cirrus Logic 功能描述:Enhanced Universal Platform System-on-Chip Processor |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。