- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4303 > EP4S40G2F40I2 (Altera)IC STRATIX IV FPGA 230K 1517FBGA PDF資料下載

參數(shù)資料

| 型號: | EP4S40G2F40I2 |

| 廠商: | Altera |

| 文件頁數(shù): | 68/82頁 |

| 文件大小: | 0K |

| 描述: | IC STRATIX IV FPGA 230K 1517FBGA |

| 產(chǎn)品培訓模塊: | Three Reasons to Use FPGA's in Industrial Designs |

| 標準包裝: | 3 |

| 系列: | STRATIX® IV GT |

| LAB/CLB數(shù): | 9120 |

| 邏輯元件/單元數(shù): | 228000 |

| RAM 位總計: | 17544192 |

| 輸入/輸出數(shù): | 654 |

| 電源電壓: | 0.92 V ~ 0.98 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | -40°C ~ 100°C |

| 封裝/外殼: | 1517-BBGA |

| 供應(yīng)商設(shè)備封裝: | 1517-FBGA(40x40) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁當前第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁

1–62

Chapter 1: DC and Switching Characteristics for Stratix IV Devices

I/O Timing

Stratix IV Device Handbook

March 2014

Altera Corporation

Volume 4: Device Datasheet and Addendum

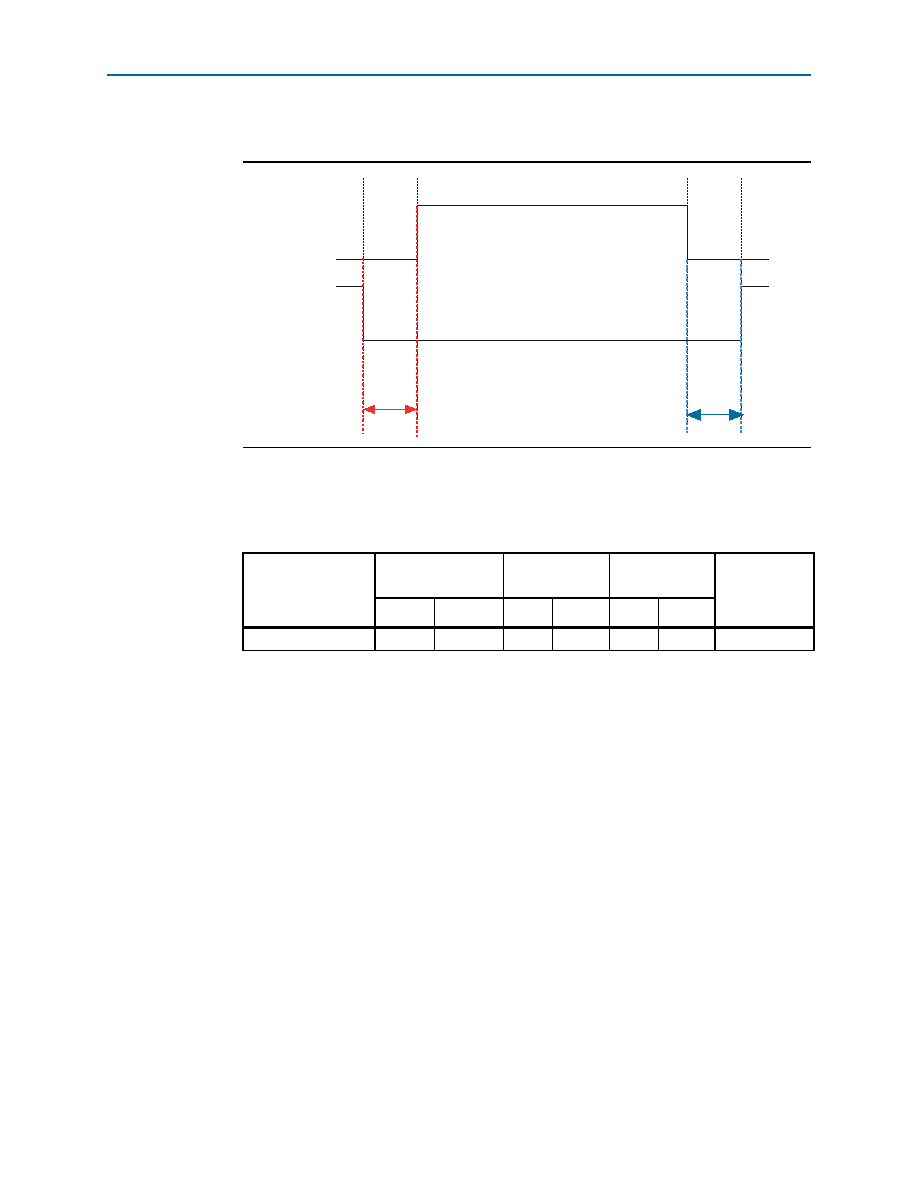

Figure 1–7 shows the timing diagram for the oe and dyn_term_ctrl signals.

Duty Cycle Distortion (DCD) Specifications

Table 1–51 lists the worst-case DCD for Stratix IV devices.

I/O Timing

Altera offers two ways to determine I/O timing—the Excel-based I/O Timing and the

Quartus II Timing Analyzer.

Excel-based I/O Timing provides pin timing performance for each device density and

speed grade. The data is typically used prior to designing the FPGA to get an estimate

of the timing budget as part of the link timing analysis. The Quartus II Timing

Analyzer provides a more accurate and precise I/O timing data based on the specifics

of the design after you complete place-and-route.

f The Excel-based I/O Timing spreadsheet is downloadable from the Literature:

Stratix IV Devices webpage.

Figure 1–7. Timing Diagram for the oe and dyn_term_ctrl Signals

Table 1–51. Worst-Case DCD on Stratix IV I/O Pins (1)

Symbol

–2/–2×

Speed Grade

–3

Speed Grade

–4

Speed Grade

Unit

Min

Max

Min

Max

Min

Max

Output Duty Cycle

45

55

45

55

45

55

%

Note to Table 1–51:

(1) The listed specification is only applicable to the output buffer across different I/O standards.

dyn_term_ctrl

oe

RX

Tristate

TX

TRS_RT

TRS_RT

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EP4SE530F43I3 | IC STRATIX IV FPGA 530K 1760FBGA |

| EP4SE530F43C2 | IC STRATIX IV FPGA 530K 1760FBGA |

| EP4SE820H35C3N | IC STRATIX IV FPGA 820K 1152HBGA |

| EP4SE820H35I4N | IC STRATIX IV FPGA 820K 1152HBGA |

| EP2S180F1508I4 | IC STRATIX II FPGA 180K 1508FBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EP4S40G2F40I2N | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Stratix IV 9120 LABs 654 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4S40G2F40I3 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Stratix IV 9120 LABs 654 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4S40G2F40I3N | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Stratix IV 9120 LABs 654 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4S40G5H40C2NES1 | 制造商:Altera Corporation 功能描述:IC FPGA 654 I/O 1517HBGA |

| EP4S40G5H40I1 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Stratix IV 21248 LABs 654 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。