- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄299032 > EP20K400ERC240-3 (ALTERA CORP) LOADABLE PLD, PQFP240 PDF資料下載

參數(shù)資料

| 型號: | EP20K400ERC240-3 |

| 廠商: | ALTERA CORP |

| 元件分類: | PLD |

| 英文描述: | LOADABLE PLD, PQFP240 |

| 封裝: | HEAT SINK, POWER, QFP-240 |

| 文件頁數(shù): | 38/65頁 |

| 文件大小: | 781K |

| 代理商: | EP20K400ERC240-3 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁當前第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁

Altera Corporation

65

Preliminary Information

APEX 20K Programmable Logic Device Family Data Sheet

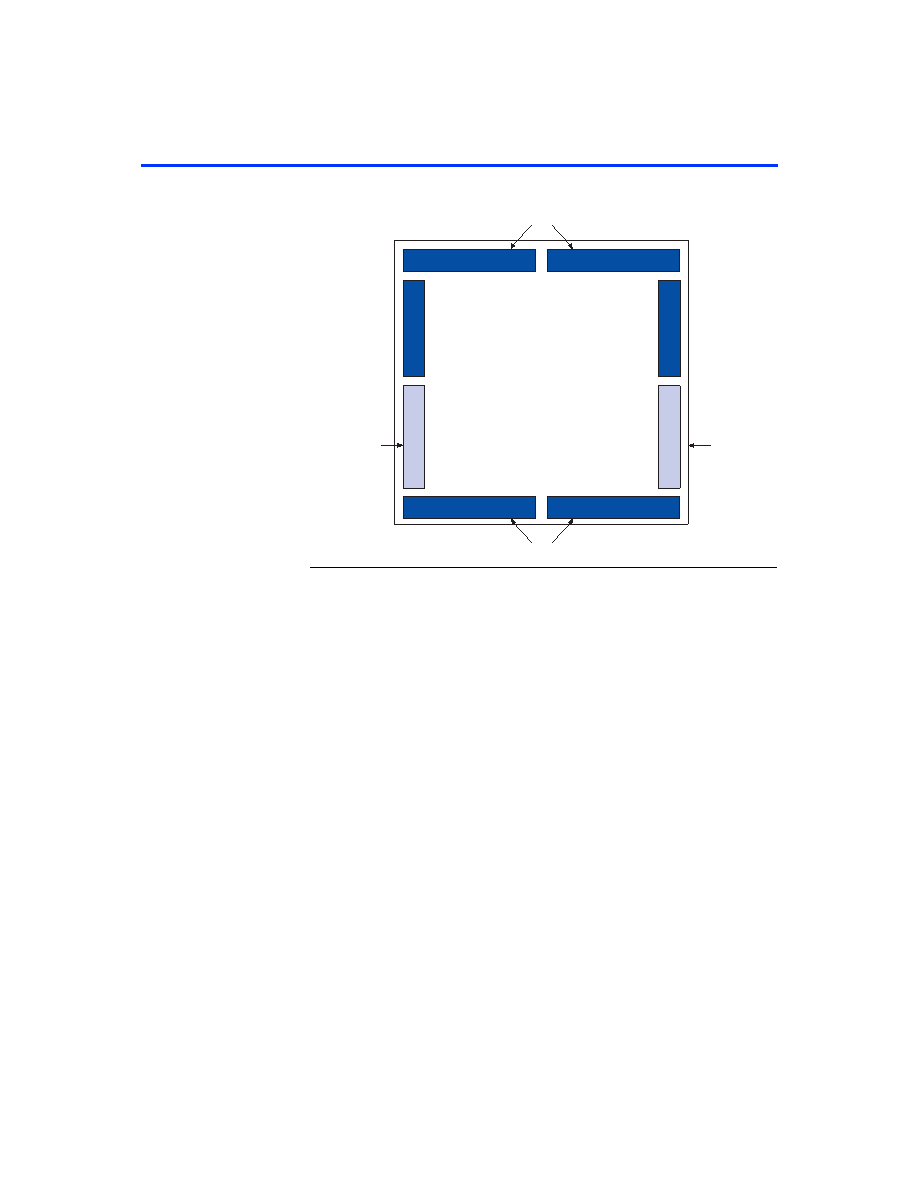

Figure 29. APEX 20KE I/O Blocks

Power Sequencing & Hot Socketing

Because APEX 20K devices can be used in a mixed-voltage environment,

they have been designed specifically to tolerate any possible power-up

sequence. Therefore, the VCCIO and VCCINT power planes may be

powered in any order.

Signals can be driven into APEX 20K devices before and during power up

without damaging the device. In addition, APEX 20K devices do not drive

out during power up. Once operating conditions are reached and the

device is configured, APEX 20K devices operate as specified by the user.

SameFrame

Pin-Outs

APEX 20K devices support the SameFrame pin-out feature for

FineLine BGA packages. The SameFrame pin-out feature is the

arrangement of balls on FineLine BGA packages such that the lower-ball-

count packages form a subset of the higher-ball-count packages.

SameFrame pin-outs provide the flexibility to migrate not only from

device to device within the same package, but also from one package to

another. A given printed circuit board (PCB) layout can support multiple

device density/package combinations. For example, a single board layout

can support a range of devices from an EP20K100 device in a 324-pin

FineLine BGA package to an EP20K400 device in a 672-pin

FineLine BGA package.

I/O Blocks

LVDS Output

Block or I/O

Block

LVDS Input

Block or I/O

Block

I/O Blocks

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EP20K400ERI240-1 | LOADABLE PLD, PQFP240 |

| EP20K400ERI240-2 | LOADABLE PLD, PQFP240 |

| EP20K400ERI240-3 | LOADABLE PLD, PQFP240 |

| EP20K400FC672-3X | LOADABLE PLD, 3.6 ns, PBGA672 |

| EPB5065G | 42 MHz, LOW PASS FILTER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EP20K400FC672-1 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 CPLD - APEX 20K 1664 Macros 502 IO RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP20K400FC672-1ES | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FPGA |

| EP20K400FC672-1X | 功能描述:FPGA - 現(xiàn)場可編程門陣列 CPLD - APEX 20K 1664 Macros 502 IO RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP20K400FC672-2 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 CPLD - APEX 20K 1664 Macros 502 IO RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP20K400FC672-2ES | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FPGA |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。