- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄362685 > EM785842P (ELAN Microelctronics Corp .) 8-BIT MICRO-CONTROLLER PDF資料下載

參數(shù)資料

| 型號: | EM785842P |

| 廠商: | ELAN Microelctronics Corp . |

| 英文描述: | 8-BIT MICRO-CONTROLLER |

| 中文描述: | 8位微控制器 |

| 文件頁數(shù): | 22/45頁 |

| 文件大?。?/td> | 461K |

| 代理商: | EM785842P |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁當(dāng)前第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁

EM785840/5841/5842

8-bit Micro-controller

__________________________________________________________________________________________________________________________________________________________________

* This specification is subject to change without notice.

2004/11/10 V1.2

ADCLK1 ADCLK0

Sampling rate

Operation voltage

0

0

1

1

0

1

0

1

83.3K

41.7K

20.8K

10.4K

>=3.5V

>=3.0V

>=2.5V

>=2.5V

* Please avoid AD converter rate over 50K Hz, it maybe decrease ADC’s resolution.

This is a CMOS multi-channel 10-bit successive approximation A/D converter.

Features

74.6kHz maximum conversion speed (Crystal mode) at 5V.

Adjusted full scale input

Internal (VDD) reference voltage

8 analog inputs multiplexed into one A/D converter

Power down mode for power saving

A/D conversion complete interrupt

Interrupt register, A/D control and status register, and A/D data register

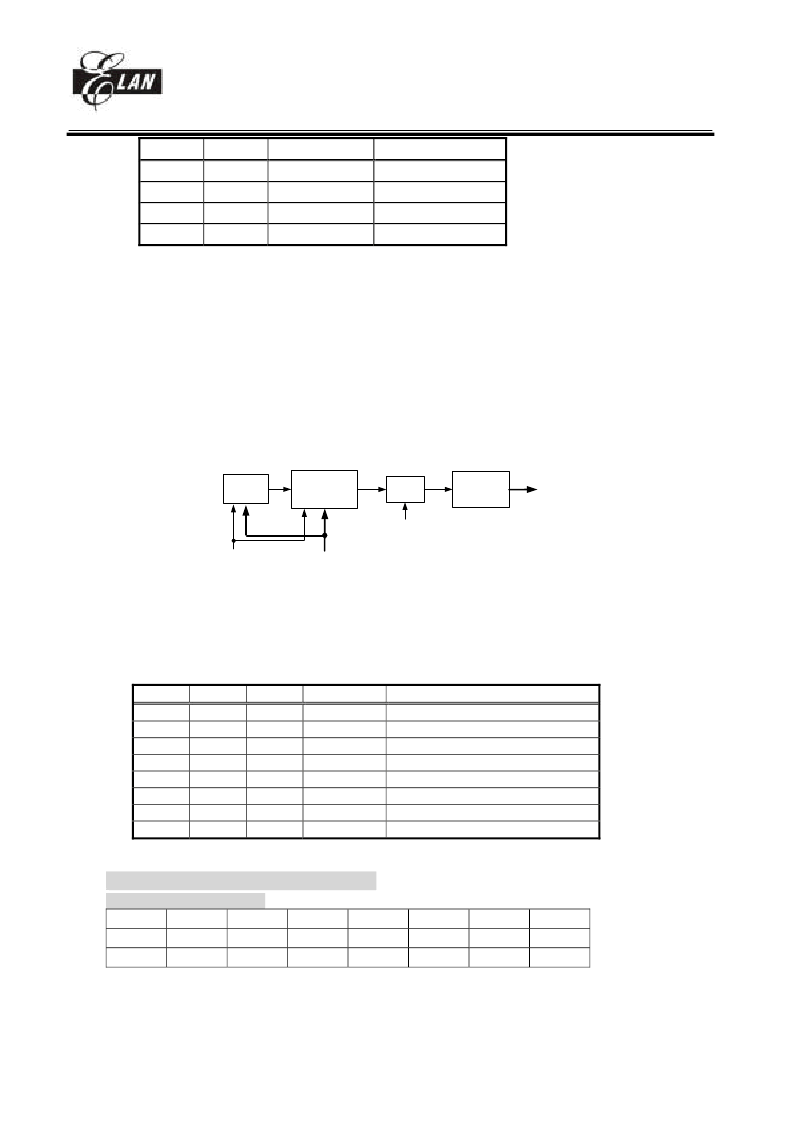

Fig.6 ADC voltage control logic

Bit 5 ~ Bit 7(IN0~ IN2) : Input channel selection of AD converter

These two bits can choose one of three AD input.

IN2

IN1

IN0

0

0

0

0

0

1

0

1

0

0

1

1

1

0

0

1

0

1

1

1

0

1

1

1

*Before switch to the AD channel, please set the corresponding pin as AD input.

IOCC (PORTC I/O control, ADC control)

PAGE0 (PORTC I/O control)

7

6

5

4

X

X

X

X

-

-

-

-

Bit 1 ~ Bit 2 (IOCC1 ~ IOCC2) : PORTC(1~2) I/O direction control register

0

put the relative I/O pin as output

1

put the relative I/O pin into high impedance

Input

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

Pin

P90

P91

P62

P63

P64

P65

P92

P93

3

X

-

2

1

0

X

-

IOCC2

R/W-1

IOCC1

R/W-1

Programmable

divider

1/Mx

Divider

Nx

10-bit

ADC

ADCLK1~ADCLK0

fs

ADC output

PLL

ENPLL

CLK2 ~ CLK0

fpll

fadc

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EM78611 | Universal Serial Bus Microcontroller Series |

| EM78800 | 8-BIT MICRO-CONTROLLER |

| EM78P811 | 8-BIT MICRO-CONTROLLER |

| EM78803 | 8-BIT MICRO-CONTROLLER |

| EM78803A | Low-Cost Molded VRS Sensor, 7,4 mm [0.292 in] |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EM78611 | 制造商:EMC 制造商全稱:ELAN Microelectronics Corp 功能描述:USB & PS/2 Keyboard Encoder |

| EM78612 | 制造商:EMC 制造商全稱:ELAN Microelectronics Corp 功能描述:Universal Serial Bus Microcontroller |

| EM78701 | 制造商:TE Connectivity 功能描述: |

| EM78800 | 制造商:EMC 制造商全稱:ELAN Microelectronics Corp 功能描述:8-BIT MICRO-CONTROLLER |

| EM78803 | 制造商:EMC 制造商全稱:ELAN Microelectronics Corp 功能描述:8-BIT MICRO-CONTROLLER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。