- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄2067 > DS1843D+ (Maxim Integrated Products)IC CIRCUIT SAMPLE-N-HOLD 8-UDFN PDF資料下載

參數(shù)資料

| 型號(hào): | DS1843D+ |

| 廠商: | Maxim Integrated Products |

| 文件頁(yè)數(shù): | 7/8頁(yè) |

| 文件大小: | 0K |

| 描述: | IC CIRCUIT SAMPLE-N-HOLD 8-UDFN |

| 產(chǎn)品培訓(xùn)模塊: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 類(lèi)型: | 采樣和保持 |

| 應(yīng)用: | 光纖學(xué)網(wǎng)絡(luò) |

| 安裝類(lèi)型: | 表面貼裝 |

| 封裝/外殼: | 8-WFDFN |

| 供應(yīng)商設(shè)備封裝: | 8-uDFN(2x2) |

| 包裝: | 管件 |

DS1843

Fast Sample-and-Hold Circuit

_______________________________________________________________________________________

7

Applications Information

Power-Supply Decoupling

To achieve the best results when using the DS1843,

decouple the power-supply pin, VCC, with a 0.01F or

0.1F capacitor. Use a high-quality X7R or equivalent

ceramic surface-mount capacitor.

DS1843 Estimated Settling Time

The settling time is dependent on the gain ratio of the

current mirror used at the input of the DS1843. For

example, the MAX4007 includes a 10:1 ratio current

mirror. This requires a 5k

resistor to create a 1V full-

scale output with 2mA current input to the MAX4007.

This resistor can be decreased to 2.5k

by using the

DS1842, which has a 5:1 ratio current mirror.

Variable Definitions:

RIN: Input resistor. The current mirror creates a voltage

across this resistor.

RSW: Resistance of series switch that connects internal

circuitry to input pins after tIST time.

CIN: 7pF parasitic (ESD) capacitor.

CPAR: External parasitic capacitance. A current mirror's

output and typical trace capacitance are less than

10pF.

CS: 5pF sample capacitor.

tIST: Internal settling time based on tS from the AC elec-

trical specification. The minimum tS includes one time

constant. tIST removes this time constant.

tRC: RC settling time of the input.

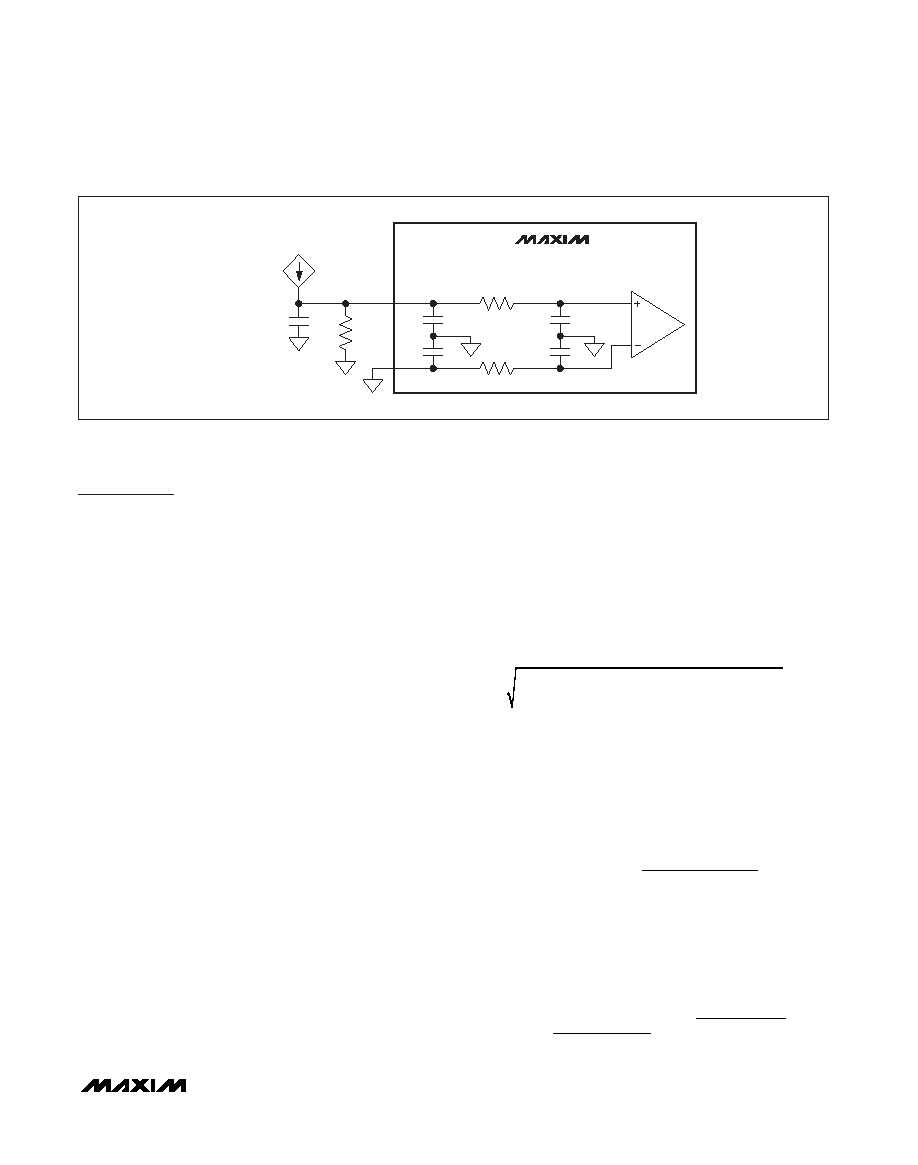

Figure 1 shows the simplified diagram of input imped-

ances for settling time calculations. Sample time is

divided into two parts:

1) tIST: Internal settling time (max 250ns). During this

time, voltage VIN (VINP - VINN) rises with a time con-

stant of:

RIN x (CIN + CPAR)

2) tRC: During this period two things happen:

a. Input VIN keeps increasing from its value at tIST

to its final value with a new time constant of:

b. RSW and CS track this VIN (input) with a time con-

stant of RSW x CS, which is 12.5ns (worst case).

Example:

Approximate accuracy calculations can be done for an

input voltage based on the above impedance values.

These calculations can be divided into three parts.

1) Accuracy of input at tIST (250ns):

where t1 = tIST = 250ns.

At tIST the internal circuit tags input impedance.

This causes charge redistribution to occur, which

causes a dip in the input voltage. The worst-case

value of the input voltage at tIST is:

V

C

CC

C

e

IN

t

S

IN

PAR

S

t

IST

@

=

++

()

×

11

R

RC

C

IN

PAR

V

×+

()

×

Accuracy

e

t

RC

C

IN

PAR

=

×+

()

1

RC

C

R

C

IN

PAR

SW

S

×+

()

() +×

()

2

DS1843

CS

CIN

CPAR

CIN

INPUT MODEL

RSW

VINP

VINN

RSW

RIN

CURRENT

MIRROR OUTPUT

Figure 1. Input Impedances for Settling Time Calculations Diagram

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DS21602N+ | IC ADAPTER CLOCK RATE 8-DIP |

| DS21610SN+ | IC ADAPT CLK RATE 3.3V/5V 16SOIC |

| DS2165Q+T&R | IC PROC ADPCM 16/24/32K 28-PLCC |

| DS2450S+T&R | IC CONVERTER A/D QUAD 1-W 8-SOIC |

| DS3508E+ | IC GAMMA BUFFER 8CH 20-TSSOP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DS1843D TRL | 制造商:MAXIM 制造商全稱(chēng):Maxim Integrated Products 功能描述:Fast Sample-and-Hold Circuit |

| DS1843D+ | 功能描述:采樣&保持放大器 Fast Sample & Hold Circuit RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 捕獲時(shí)間:20 us 電源電壓-最大:18 V 最大工作溫度:+ 85 C 最小工作溫度:- 25 C 安裝風(fēng)格: 封裝 / 箱體:SOIC-14 封裝:Tube |

| DS1843D+TRL | 功能描述:采樣&保持放大器 Fast Sample & Hold Circuit RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 捕獲時(shí)間:20 us 電源電壓-最大:18 V 最大工作溫度:+ 85 C 最小工作溫度:- 25 C 安裝風(fēng)格: 封裝 / 箱體:SOIC-14 封裝:Tube |

| DS1843K | 功能描述:放大器 IC 開(kāi)發(fā)工具 Fast Sample & Hold Circuit RoHS:否 制造商:International Rectifier 產(chǎn)品:Demonstration Boards 類(lèi)型:Power Amplifiers 工具用于評(píng)估:IR4302 工作電源電壓:13 V to 23 V |

| DS1844 | 制造商:DALLAS 制造商全稱(chēng):Dallas Semiconductor 功能描述:Quad Digital Potentiometer |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。