- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376760 > DM4M32SJ-10 Enhanced DRAM (EDRAM) Module PDF資料下載

參數(shù)資料

| 型號: | DM4M32SJ-10 |

| 英文描述: | Enhanced DRAM (EDRAM) Module |

| 中文描述: | 增強的DRAM(eDRAM內存)模塊 |

| 文件頁數(shù): | 9/21頁 |

| 文件大?。?/td> | 124K |

| 代理商: | DM4M32SJ-10 |

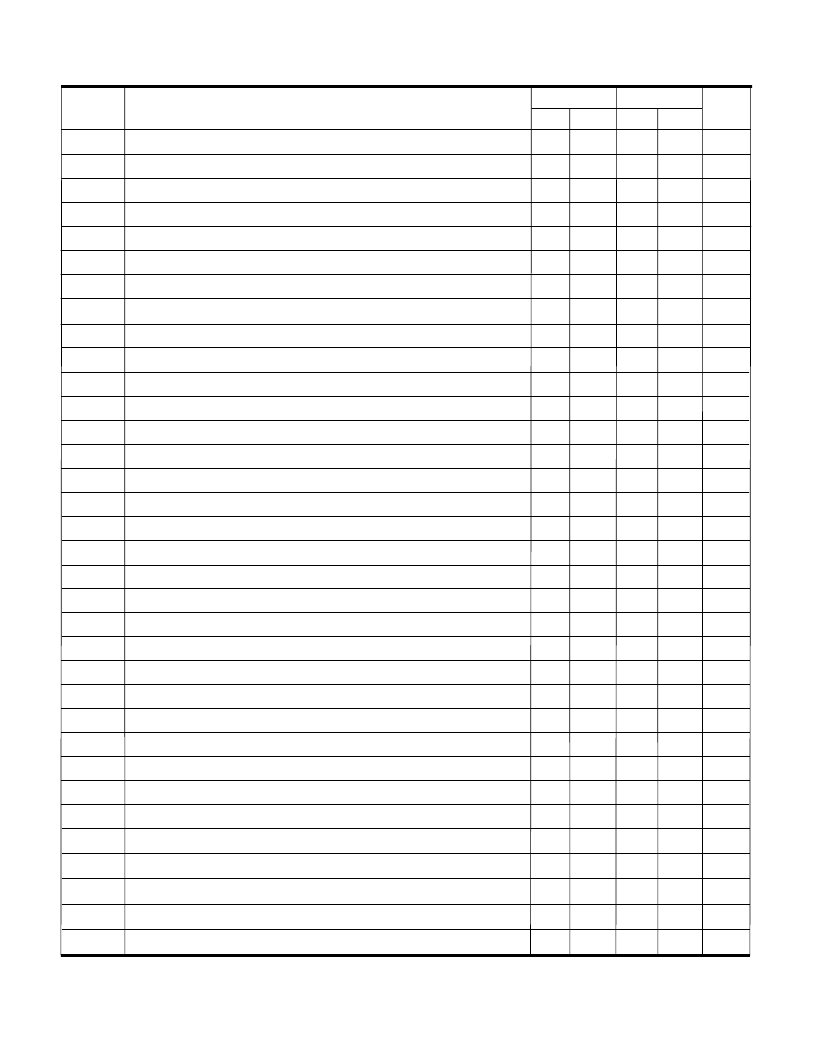

2-43

Symbol

Description

t

RGX

t

RQX1(2,5)

t

RP

t

RP1

t

RRH

t

RSH

Output Enable Don't Care From Row Enable (Write, Cache Miss), DQ = Hi-Z

Row Precharge Time

Row Precharge Time, Cache Hit (Row=LRR) Read Cycle

Write Enable Don’t Care From Row Enable (Write Only)

Last Write Address Latch to End of Write

Row Enable to Column Address Latch Low For Second Write

9

0

20

8

0

ns

ns

ns

ns

ns

ns

Min

Max

Units

35

25

10

0

Min

Max

10

Row Enable High to Output Turn-On After Write Miss

12

ns

15

40

-12

-15

12

15

t

RSW

t

RWL

Last Write Enable to End of Write

ns

12

15

t

SC

t

SHR

Column Address Cycle Time

ns

12

15

Select Hold From Row Enable

ns

0

0

t

SQV

(1)

t

SQX

(2,3)

t

SQZ

(4,5)

Chip Select Access Time

ns

12

15

Output Turn-On From Select Low

ns

12

15

0

0

Output Turn-Off From Chip Select

ns

8

10

0

0

t

SSR

Select Setup Time to Row Enable

ns

5

5

t

T

Transition Time (Rise and Fall)

ns

10

10

1

1

t

WC

Write Enable Cycle Time

ns

12

15

t

WCH

t

WHR

(6)

Column Address Latch Low to Write Enable Inactive Time

ns

5

5

t

WI

Write Enable Inactive Time

ns

5

5

t

WP

t

WQV

(1)

Write Enable Active Time

ns

t

WQX

(2,5)

Data Output Turn-On From Write Enable High

ns

0

Data Valid From Write Enable High

ns

0

12

5

5

5

15

12

15

t

RE1

t

REF

Row Enable Active Time, Cache Hit (Row=LRR) Read Cycle

Refresh Period

ms

64

64

8

10

ns

Write Enable Hold After /RE

ns

0

0

t

RAC

(1)

t

RAC1

(1)

t

RAH

Row Enable Access Time, On a Cache Miss

30

35

ns

Row Enable Access Time, On a Cache Hit (Limit Becomes t

AC

)

Row Address Hold Time

15

17

ns

1

1.5

ns

t

RE

Row Enable Active Time

30

35

ns

100000

100000

t

QL

QLE Low Time

5

5

ns

t

QQH

Data Hold From QLE Inactive

2

2

ns

t

QQV

Data Valid From QLE Low

7.5

7.5

ns

Data Turn-Off From Write Enable Low

ns

0

0

5

12

15

15

t

WQZ

(3,4)

(1) VOUT Timng Reference Point at 1.5V; (2) Parameter Defines Time When Output is Enabled (Sourcing or Sinking Current) and is Not Referenced to VOH or VOL; (3) MnimumSpecification is Referenced fromVIH and Maximum

Specification is Referenced fromVIL on Input Control Signal; (4) Parameter Defines Time When Output Achieves Open-Circuit Condition and is Not Referenced to VOH or VOL; (5) MnimumSpecification is Referenced fromVIL and

MaximumSpecification is Referenced fromVIH on Input Control Signal; (6) On DM2213, tWHR Mnimumis tDS

t

WRP

t

WRR

Write Enable Setup Time to Row Enable

Write to Read Recovery (Following Write Miss)

12

ns

ns

Switching Characteristics (continued)

V

CC

= 5V ± 5%, T

A

= 0 to 70°C(Commercial), -40 to 85°C (Industrial), C

L

= 50pf

相關PDF資料 |

PDF描述 |

|---|---|

| DM2203T-20 | Enhanced DRAM (EDRAM) |

| DM2203TME-15 | Enhanced DRAM (EDRAM) |

| DM2203TME-20 | Enhanced DRAM (EDRAM) |

| DM2212J-10 | Enhanced DRAM (EDRAM) |

| DM1M32SJ6-10 | Enhanced DRAM (EDRAM) Module |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| DM4PRTR | 制造商:Siemens 功能描述: |

| DM4S6B00F/17 | 制造商:NXP Semiconductors 功能描述:DVD-R 16X 100PK Spindle 制造商:NXP Semiconductors 功能描述:DVD-R 16X SPINDLE 100PK |

| DM4S6B25F/17 | 制造商:NXP Semiconductors 功能描述:DVD-R 16X 25PK Spindle 制造商:NXP Semiconductors 功能描述:DVD-R 16X SPINDLE 25PK |

| DM4S6B50F/17 | 制造商:NXP Semiconductors 功能描述:DVD-R 16X 50PK Spindle |

| DM4T1200 | 制造商:Lovato Electric Inc 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。