- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄376632 > DEM-VSP2232Y (Texas Instruments, Inc.) CCD SIGNAL PROCESSOR FOR DIGITAL CAMERAS PDF資料下載

參數(shù)資料

| 型號(hào): | DEM-VSP2232Y |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | CCD SIGNAL PROCESSOR FOR DIGITAL CAMERAS |

| 中文描述: | CCD信號(hào)處理器的數(shù)碼相機(jī) |

| 文件頁(yè)數(shù): | 7/19頁(yè) |

| 文件大小: | 248K |

| 代理商: | DEM-VSP2232Y |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)當(dāng)前第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)

VSP2232

SLAS320

–

MAY 2001

7

www.ti.com

optical black (OB) level clamp loop (continued)

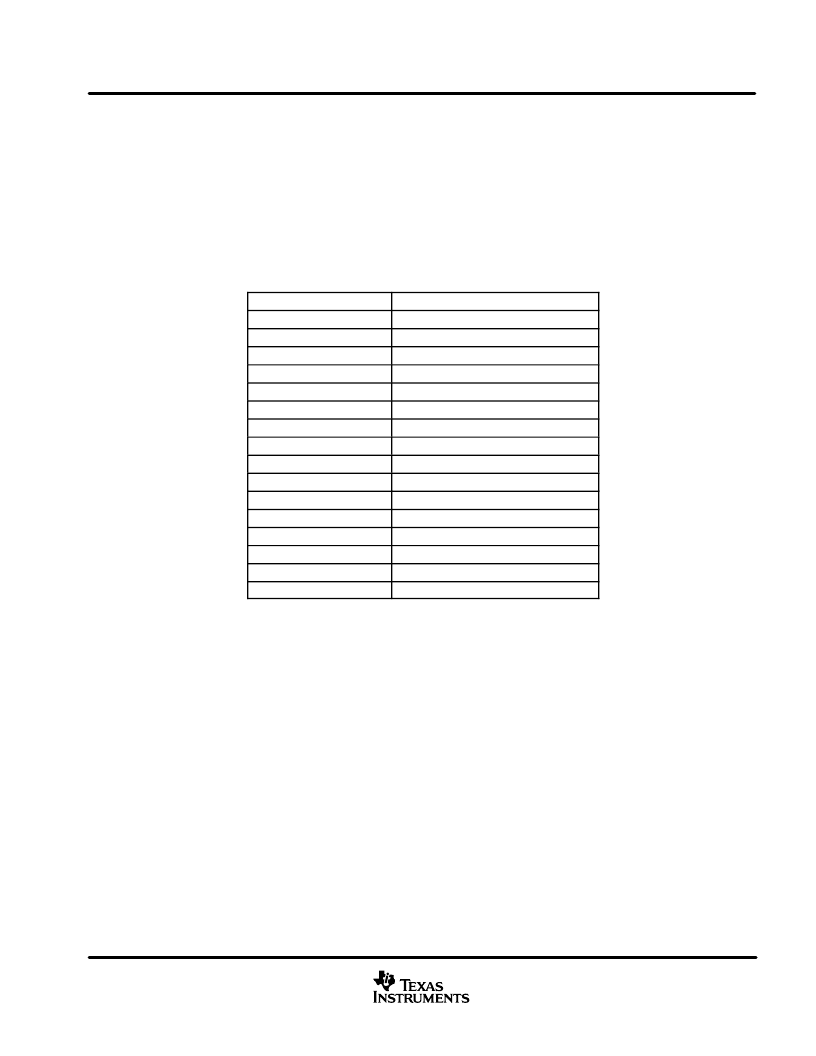

The OB clamp level (the pedestal level) is programmable through the serial interface, refer to

serial interface

for details. Table 1 shows the relationship between the input code and the OB clamp level.

The active polarity of CLPOB (active high or active low) can be chosen through the serial interface, refer to

serial

interface

for details. The default value of CLPOB is active low.

However, right after power on, this value is unknown. For this reason, it must be set to the appropriate value

by using the serial interface, or reset to the default value by the RESET pin. The description and the timing

diagrams in this data sheet are all based on the polarity of active low (default value).

Table 1. Programmable OB Clamp Level

INPUT CODE

OB CLAMP LEVEL, LSBs of 12-Bits

0000

2 LSB

0001

18 LSB

0010

34 LSB

0011

50 LSB

0100

66 LSB

0101

82 LSB

0110

98 LSB

0111

114 LSB

1000 (Default)

130 LSB

1001

146 LSB

1010

162 LSB

1011

178 LSB

1100

194 LSB

1101

210 LSB

1110

226 LSB

1111

242 LSB

preblanking and data latency

Some CCDs have large transient output signals during blanking intervals. Such signals may exceed the

VSP2232

’

s 1-V

P

–

P

input signal range and would overdrive the VSP2232 into saturation. Recovery time from

the saturation could be substantial. To avoid this, the VSP2232 has an input blanking (or preblanking) function.

When PBLK goes to low, the CCDIN input is disconnected from the internal CDS stage and large transients are

prevented from passing through. The VSP2232

’

s digital outputs will go to all zeros at the 11th rising edge of

ADCCK from just after PBLK set to low to accommodate the clock latency of the VSP2232. In this mode, the

digital output data comes out at the rising edge of ADCCK with a delay of 11 clock cycles (data latency is 11).

In the normal operation mode, it is different from the preblanking mode. The digital output data comes out at

the rising edge of ADCCK with a delay of nine clock cycles (data latency is 9).

In order to keep stable and accurate OB clamp level, CLPOB should not be activated during PBLK active period.

Since CCDIN input is disconnected from the internal circuit, even if the autocalibration loop should be closed

while CLPOB is active. Then the OB clamp level is different from the actual OB level established by the CCD

imager output. The missed OB clamp level would affect the picture quality.

If the input voltage is higher than the supply rail by 0.3 V or lower than the ground rail by 0.3 V, the protection

diodes will be turned on to prevent the input voltage from going further. Such a high swing signal may cause

a device damage to the VSP2232 and should be avoided.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DEM16101H | LCD MODULE |

| DEM16101SYH | DEM16101SYH |

| DEM16216SYH-LY | DEM16216SYH-LY |

| DEM16216SYH-PY | Display Elektronik GmbH |

| DEM16217SYH | Display Elektronik GmbH |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DEM-VSP2260Y | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| DEM-VSP2262Y | 制造商:Texas Instruments 功能描述:EVAL BD FOR CCD SGNL PROCESSOR FOR DGTL CAMERAS - Bulk |

| DEM-VSP3100Y | 制造商:Texas Instruments 功能描述:EVALUATION/DEMO BOARD FOR VSP3100Y - Bulk |

| DEMX-5W1P-1AON-K87 | 制造商:ITT Interconnect Solutions 功能描述:DEMX-5W1P-1AON-K87 - Bulk |

| DEMX5W1PK87 | 制造商:ITT 功能描述:DSUB 5W1 M PCR/A G50 T 制造商:ITT Interconnect Solutions 功能描述:DSUB 5W1 M PCR/A G50 T |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。