- 您現(xiàn)在的位置:買賣IC網 > PDF目錄19023 > DC1370A-J (Linear Technology)BOARD DEMO 65MSPS LTC2258-12 PDF資料下載

參數資料

| 型號: | DC1370A-J |

| 廠商: | Linear Technology |

| 文件頁數: | 31/34頁 |

| 文件大小: | 0K |

| 描述: | BOARD DEMO 65MSPS LTC2258-12 |

| 軟件下載: | QuikEval II System |

| 設計資源: | DC1370A Design Files |

| 標準包裝: | 1 |

| 系列: | * |

| 相關產品: | DC718C-ND - DEMO QUIKEVAL-II DATA |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁當前第31頁第32頁第33頁第34頁

LTC2258-12

LTC2257-12/LTC2256-12

6

225812fd

For more information www.linear.com/LTC2258-12

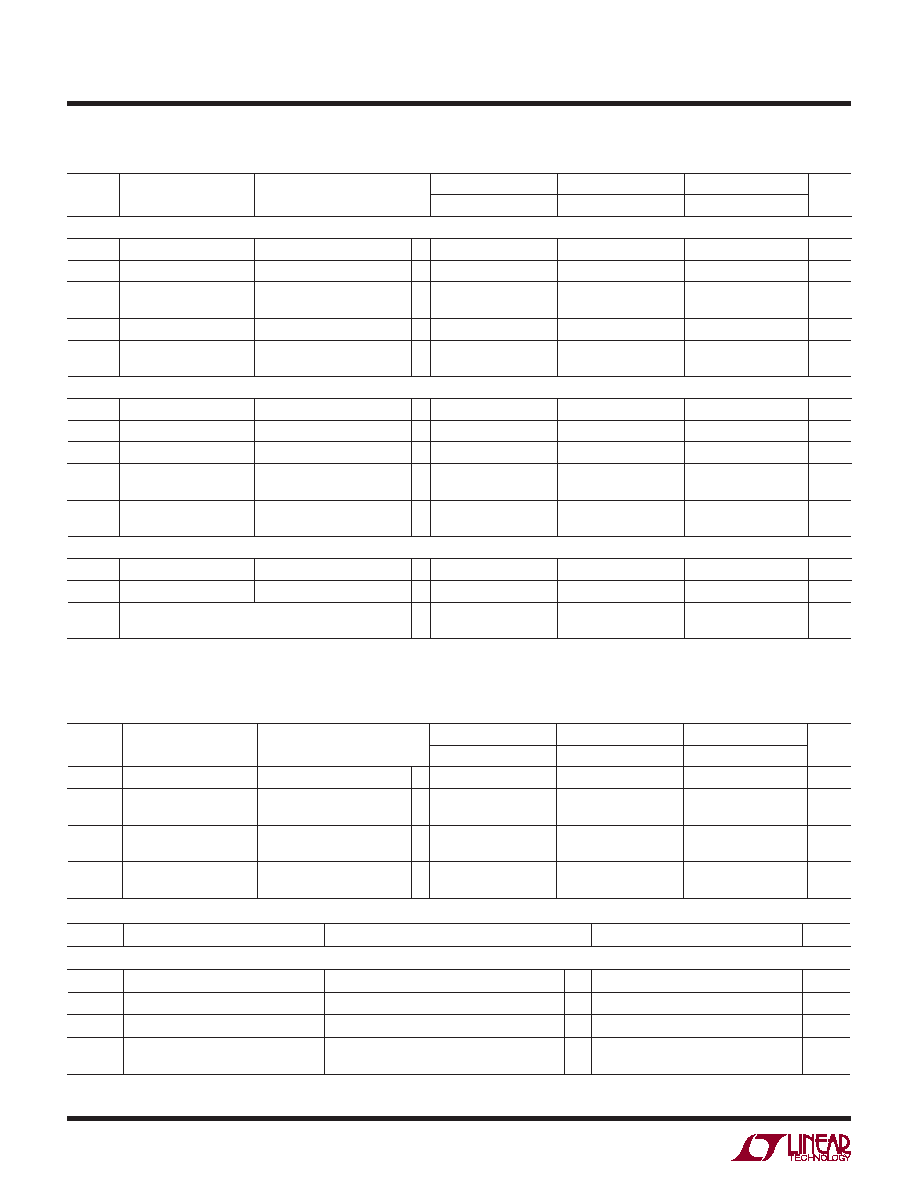

power requireMenTs The

l

denotes the specifications which apply over the full operating temperature

range, otherwise specifications are at TA = 25°C. (Note 9)

SYMBOL PARAMETER

CONDITIONS

LTC2258-12

LTC2257-12

LTC2256-12

UNITS

MIN

TYP

MAX

MIN

TYP

MAX

MIN

TYP

MAX

CMOS Output Modes: Full Data Rate and Double Data Rate

VDD

Analog Supply Voltage

(Note 10)

l

1.7

1.8

1.9

1.7

1.8

1.9

1.7

1.8

1.9

V

OVDD

Output Supply Voltage

(Note 10)

l

1.1

1.9

1.1

1.9

1.1

1.9

V

IVDD

Analog Supply Current

DC Input

Sine Wave Input

l

43.6

44.2

49

26.3

27.2

30

18.9

19.1

21

mA

IOVDD

Digital Supply Current

Sine Wave Input, OVDD=1.2V

2.3

1.5

0.9

mA

PDISS

Power Dissipation

DC Input

Sine Wave Input, OVDD=1.2V

l

78.5

82.3

89

47.3

50.8

54

34

35.5

38

mW

LVDS Output Mode

VDD

Analog Supply Voltage

(Note 10)

l

1.7

1.8

1.9

1.7

1.8

1.9

1.7

1.8

1.9

V

OVDD

Output Supply Voltage

(Note 10)

l

1.7

1.9

1.7

1.9

1.7

1.9

V

IVDD

Analog Supply Current

Sine Wave Input

l

48.1

54

30.6

35

22.7

26

mA

IOVDD

Digital Supply Current

(0VDD = 1.8V)

Sine Input, 1.75mA Mode

Sine Input, 3.5mA Mode

l

18.8

36.7

21

40

18.8

36.7

21

40

18.8

36.7

21

40

mA

PDISS

Power Dissipation

Sine Input, 1.75mA Mode

Sine Input, 3.5mA Mode

l

120.4

152.6

135

170

88.9

121.1

101

135

74.7

106.9

85

119

mW

All Output Modes

PSLEEP

Sleep Mode Power

0.5

mW

PNAP

Nap Mode Power

9

mW

PDIFFCLK Power Increase with Differential Encode Mode Enabled

(No increase for Nap or Sleep Modes)

10

mW

TiMing characTerisTics The

l

denotes the specifications which apply over the full operating temperature

range, otherwise specifications are at TA = 25°C. (Note 5)

SYMBOL PARAMETER

CONDITIONS

LTC2258-12

LTC2257-12

LTC2256-12

UNITS

MIN

TYP

MAX

MIN

TYP

MAX

MIN

TYP

MAX

fS

Sampling Frequency

(Note 10)

l

1

65

1

40

1

25

MHz

tL

ENC Low Time (Note 8) Duty Cycle Stabilizer Off

Duty Cycle Stabilizer On

l

7.3

2.0

7.69

500

11.88

2.00

12.5

500

19

2.00

20

500

ns

tH

ENC High Time (Note 8) Duty Cycle Stabilizer Off

Duty Cycle Stabilizer On

l

7.3

2.0

7.69

500

11.88

2.00

12.5

500

19

2.00

20

500

ns

tAP

Sample-and-Hold

Acquisition Delay Time

0

ns

SYMBOL PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

Digital Data Outputs (CMOS Modes: Full Data Rate and Double Data Rate)

tD

ENC to Data Delay

CL = 5pF (Note 8)

l

1.1

1.7

3.1

ns

tC

ENC to CLKOUT Delay

CL = 5pF (Note 8)

l

1

1.4

2.6

ns

tSKEW

DATA to CLKOUT Skew

tD – tC (Note 8)

l

0

0.3

0.6

ns

Pipeline Latency

Full Data Rate Mode

Double Data Rate Mode

5.0

5.5

Cycles

相關PDF資料 |

PDF描述 |

|---|---|

| 17 | LAMP T1-3/4 WEDGE BASE |

| CL-830-R23-XT | CHROMALIT XT LIGHT SOURCE RND |

| 85- | T1-3/4 28V WEDGE BASE |

| 93 | LAMP INCAND S-8 S.C. BAYONET |

| A3CT-7011 | SWITCH UNIT-IP40 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| DC1370A-K | 功能描述:BOARD DEMO 40MSPS LTC2257-12 RoHS:是 類別:未定義的類別 >> 其它 系列:* 標準包裝:1 系列:* 其它名稱:MS305720A |

| DC1370A-L | 功能描述:BOARD DEMO 25MSPS LTC2256-12 RoHS:是 類別:未定義的類別 >> 其它 系列:* 標準包裝:1 系列:* 其它名稱:MS305720A |

| DC1370A-M | 制造商:Linear Technology 功能描述:14BIT ADC Eval Brd, Rq. DC718 制造商:Linear Technology 功能描述:14BIT ADC Eval Brd, Rq. DC718; Silicon Manufacturer:Linear Technology; Silicon Core Number:LTC2262-14; Kit Application Type:Data Converter; Application Sub Type:ADC; Kit Contents:Board, Guide; Features:Also works with requred DC718 |

| DC1370A-N | 制造商:Linear Technology 功能描述:12BIT ADC Eval Brd, Rq. DC718 制造商:Linear Technology 功能描述:12BIT ADC Eval Brd, Rq. DC718; Silicon Manufacturer:Linear Technology; Silicon Core Number:LTC2262-12; Kit Application Type:Data Converter; Application Sub Type:ADC; Kit Contents:Board, Guide; Features:Also works with requred DC718 |

| DC1371A | 功能描述:BOARD USB DATA ACQUISITION HS RoHS:是 類別:未定義的類別 >> 其它 系列:* 標準包裝:1 系列:* 其它名稱:MS305720A |

發(fā)布緊急采購,3分鐘左右您將得到回復。