- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379098 > CYD02S36V (Cypress Semiconductor Corp.) FLEx36TM 3.3V 32K/64K/128K/256K/512 x 36 Synchronous Dual-Port RAM(FLEx36TM 3.3V 32K/64K/128K/256K/512 x 36同步雙端口RAM) PDF資料下載

參數(shù)資料

| 型號: | CYD02S36V |

| 廠商: | Cypress Semiconductor Corp. |

| 英文描述: | FLEx36TM 3.3V 32K/64K/128K/256K/512 x 36 Synchronous Dual-Port RAM(FLEx36TM 3.3V 32K/64K/128K/256K/512 x 36同步雙端口RAM) |

| 中文描述: | FLEx36TM 3.3 32K/64K/128K/256K/512 × 36同步雙口RAM(FLEx36TM 3.3 32K/64K/128K/256K/512 × 36同步雙端口RAM)的 |

| 文件頁數(shù): | 24/28頁 |

| 文件大?。?/td> | 608K |

| 代理商: | CYD02S36V |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當(dāng)前第24頁第25頁第26頁第27頁第28頁

CYD01S36V

CYD02S36V/CYD04S36V

CYD09S36V/CYD18S36V

Document #: 38-06076 Rev. *E

Page 24 of 28

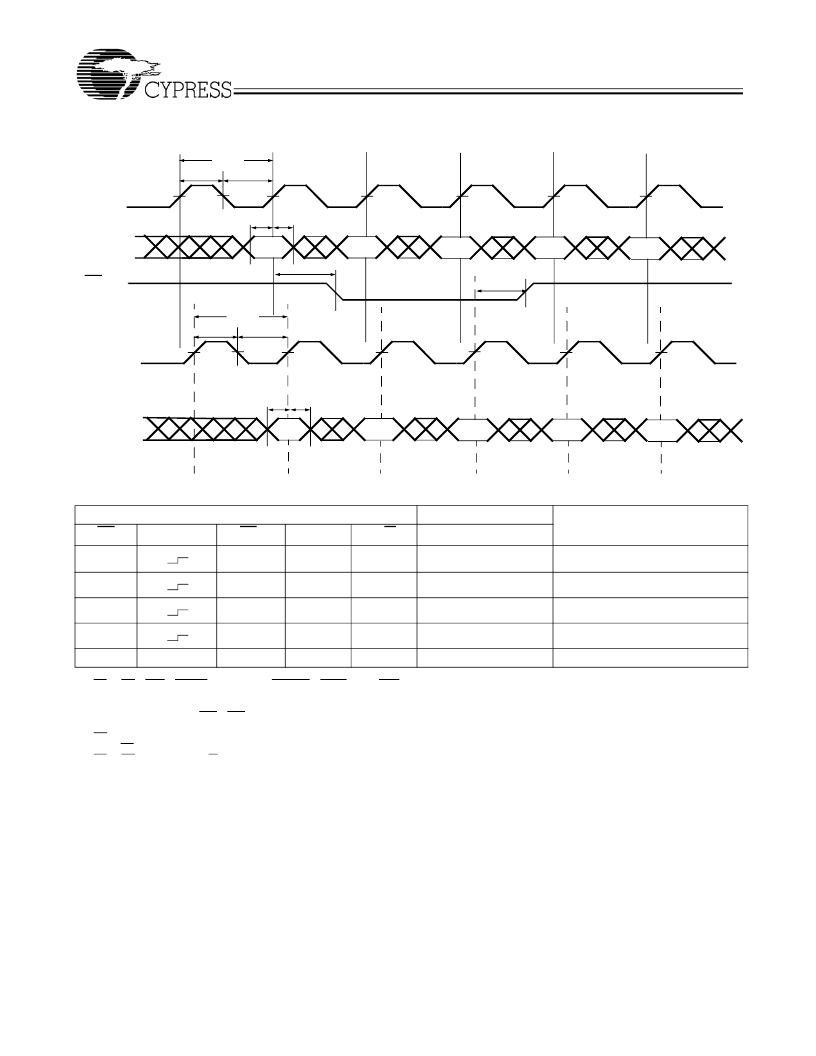

MailBox Interrupt Timing

[57, 58, 59, 60, 61]

Switching Waveforms

(continued)

t

CH2

t

CL2

t

CYC2

CLK

L

t

CH2

t

CL2

t

CYC2

CLK

R

7FFFF

t

SA

t

HA

A

n+3

A

n

A

n+1

A

n+2

L_PORT

ADDRESS

A

m

A

m+4

A

m+1

7FFFF

A

m+3

R_PORT

ADDRESS

INT

R

t

SA

t

HA

t

SINT

t

RINT

Table 7. Read/Write and Enable Operation

(Any Port)

[1, 18, 62, 63, 64]

Inputs

Outputs

Operation

OE

X

CLK

CE

0

H

CE

1

X

R/W

X

DQ

0

–

DQ

35

High-Z

Deselected

X

X

L

X

High-Z

Deselected

X

L

H

L

D

IN

Write

L

L

H

H

D

OUT

Read

H

X

L

H

X

High-Z

Outputs Disabled

Notes:

57.CE

= OE = ADS = CNTEN = LOW; CE

= CNTRST = MRST = CNT/MSK = HIGH.

58.Address “7FFFF” is the mailbox location for R_Port of the 9-Mbit device.

59.L_Port is configured for Write operation, and R_Port is configured for Read operation.

60.At least one byte enable (BE0 – BE3) is required to be active during interrupt operations.

61.Interrupt flag is set with respect to the rising edge of the Write clock, and is reset with respect to the rising edge of the Read clock.

62.OE is an asynchronous input signal.

63.When CE changes state, deselection and Read happen after one cycle of latency.

64.CE

0

= OE = LOW; CE

1

= R/W = HIGH.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CYD04S36V | FLEx36TM 3.3V 32K/64K/128K/256K/512 x 36 Synchronous Dual-Port RAM(FLEx36TM 3.3V 32K/64K/128K/256K/512 x 36同步雙端口RAM) |

| CYD09S36V | FLEx36TM 3.3V 32K/64K/128K/256K/512 x 36 Synchronous Dual-Port RAM(FLEx36TM 3.3V 32K/64K/128K/256K/512 x 36同步雙端口RAM) |

| CYD18S72V18 | FullFlex Synchronous SDR Dual-Port SRAM(FullFlex同步SDR雙端口SRAM) |

| CYD04S72V18 | FullFlex Synchronous SDR Dual-Port SRAM(FullFlex同步SDR雙端口SRAM) |

| CYD36S72V18 | FullFlex Synchronous SDR Dual-Port SRAM(FullFlex同步SDR雙端口SRAM) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CYD02S36V_11 | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:FLEx36? 3.3 V (64K x 36) Synchronous Dual-Port RAM |

| CYD02S36V_13 | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:FLEx36a?¢ 3.3 V (64K x 36) Synchronous Dual-Port RAM |

| CYD02S36V-133BBC | 制造商:Rochester Electronics LLC 功能描述:3.3V, 64K X 36 SYNCH DUAL-PORT SRAM (FLEX36 2M) - Bulk |

| CYD02S36V-133BBI | 制造商:Rochester Electronics LLC 功能描述:3.3V, 64K X 36 SYNCH DUAL-PORT SRAM (FLEX36 2M) - Bulk |

| CYD02S36V-167BBC | 功能描述:靜態(tài)隨機存取存儲器 2M Sync Dual Port 64K x 36 3.3V COM RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。