- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378513 > CY7C68014A (Cypress Semiconductor Corp.) EZ-USB FX2LP USB Microcontroller PDF資料下載

參數(shù)資料

| 型號(hào): | CY7C68014A |

| 廠商: | Cypress Semiconductor Corp. |

| 英文描述: | EZ-USB FX2LP USB Microcontroller |

| 中文描述: | 的EZ - USB FX2LP的USB微控制器 |

| 文件頁數(shù): | 25/55頁 |

| 文件大?。?/td> | 1958K |

| 代理商: | CY7C68014A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁當(dāng)前第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁

CY7C68013A/CY7C68014A

CY7C68015A/CY7C68016A

Document #: 38-08032 Rev. *G

Page 25 of 55

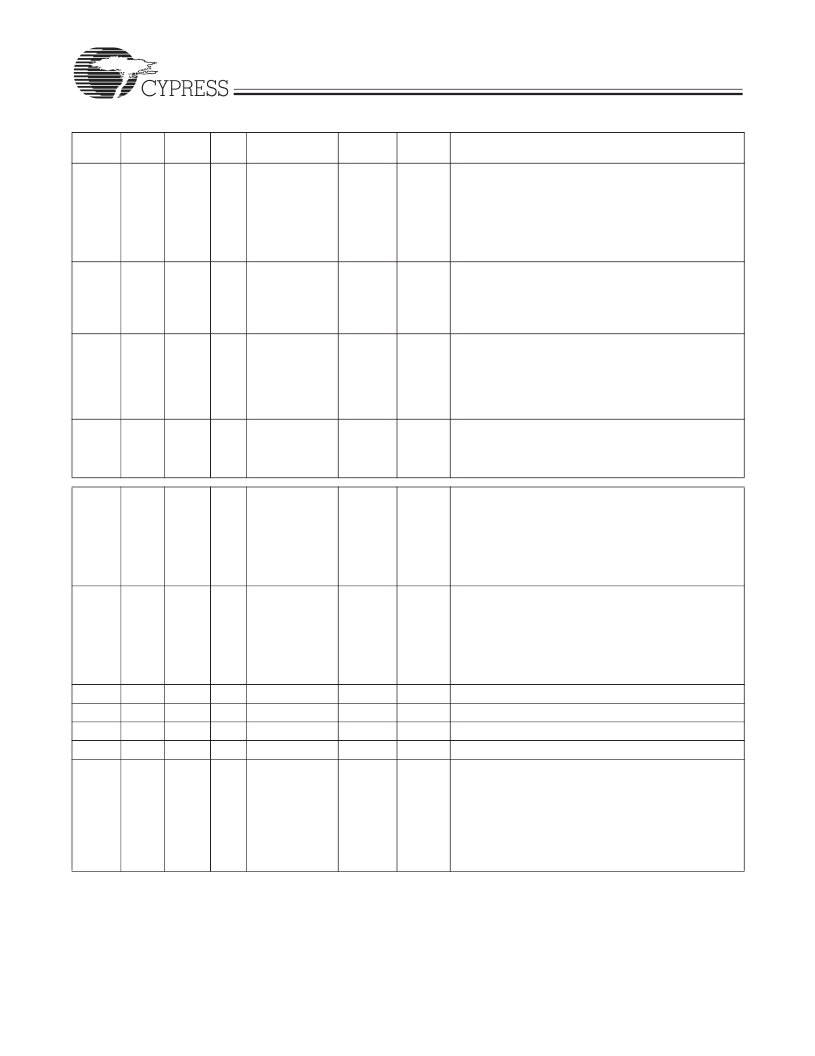

112

90

PE4 or

RXD1OUT

I/O/Z

I

(PE4)

Multiplexed pin whose function is selected by the

PORTECFG.4 bit.

PE4

is a bidirectional I/O port pin.

RXD1OUT

is an active-HIGH output from 8051 UART1.

When RXD1OUT is selected and UART1 is in Mode 0,

this pin provides the output data for UART1 only when

it is in sync mode. In Modes 1, 2, and 3, this pin is HIGH.

Multiplexed pin whose function is selected by the

PORTECFG.5 bit.

PE5

is a bidirectional I/O port pin.

INT6

is the 8051 INT6 interrupt request input signal. The

INT6 pin is edge-sensitive, active HIGH.

Multiplexed pin whose function is selected by the

PORTECFG.6 bit.

PE6

is a bidirectional I/O port pin.

T2EX

is an active-HIGH input signal to the 8051 Timer2.

T2EX reloads timer 2 on its falling edge. T2EX is active

only if the EXEN2 bit is set in T2CON.

Multiplexed pin whose function is selected by the

PORTECFG.7 bit.

PE7

is a bidirectional I/O port pin.

GPIFADR8

is a GPIF address output pin.

113

91

PE5 or

INT6

I/O/Z

I

(PE5)

114

92

PE6 or

T2EX

I/O/Z

I

(PE6)

115

93

PE7 or

GPIFADR8

I/O/Z

I

(PE7)

4

3

8

1

RDY0 or

SLRD

Input

N/A

Multiplexed pin whose function is selected by the

following bits:

IFCONFIG[1..0].

RDY0

is a GPIF input signal.

SLRD

is the input-only read strobe with programmable

polarity (FIFOPINPOLAR.3) for the slave FIFOs

connected to FD[7..0] or FD[15..0].

Multiplexed pin whose function is selected by the

following bits:

IFCONFIG[1..0].

RDY1

is a GPIF input signal.

SLWR

is the input-only write strobe with programmable

polarity (FIFOPINPOLAR.2) for the slave FIFOs

connected to FD[7..0] or FD[15..0].

RDY2

is a GPIF input signal.

RDY3

is a GPIF input signal.

RDY4

is a GPIF input signal.

RDY5

is a GPIF input signal.

Multiplexed pin whose function is selected by the

following bits:

IFCONFIG[1..0].

CTL0

is a GPIF control output.

FLAGA

is a programmable slave-FIFO output status

flag signal.

Defaults to programmable for the FIFO selected by the

FIFOADR[1:0] pins.

5

4

9

2

RDY1 or

SLWR

Input

N/A

6

7

8

9

69

5

6

7

8

54

RDY2

RDY3

RDY4

RDY5

CTL0 or

FLAGA

Input

Input

Input

Input

O/Z

N/A

N/A

N/A

N/A

H

36

29

Table 4-1. FX2LP Pin Descriptions

(continued)

[10]

128

TQFP

100

TQFP

56

SSOP

56

QFN

Name

Type

Default

Description

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY7C68014A-56LFXC | D-SSK 110 KER |

| CY7C68014A-56PVXC | EZ-USB FX2LP USB Microcontroller |

| CY7C68015A-56LFXC | EZ-USB FX2LP USB Microcontroller |

| CY7C68013A-128AXC | CAC 2C 2#12 PIN PLUG |

| CY7C68024 | EZ-USB NX2LP USB 2.0 NAND Flash Controller(EZ-USB NX2LP USB 2.0 NAND閃存控制器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C68014A-100AXC | 功能描述:8位微控制器 -MCU EZ USB FX2LP Battery App High COM RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時(shí)鐘頻率:50 MHz 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| CY7C68014A-100AXCKJ | 制造商:Cypress Semiconductor 功能描述: |

| CY7C68014A-128AXC | 功能描述:8位微控制器 -MCU EZ USB FX2LP Battery App High COM RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時(shí)鐘頻率:50 MHz 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| CY7C68014A-56BAXC | 功能描述:8位微控制器 -MCU EZ USB FX2LP Battery PWR LO COM RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時(shí)鐘頻率:50 MHz 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| CY7C68014A-56LFXC | 功能描述:8位微控制器 -MCU EZ USB FX2LP Battery Apps LO COM RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時(shí)鐘頻率:50 MHz 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。