- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379092 > CY7C4425-25ASI (CYPRESS SEMICONDUCTOR CORP) 64/256/512/1K/2K/4K x18 Low-Voltage Synchronous FIFOs PDF資料下載

參數(shù)資料

| 型號(hào): | CY7C4425-25ASI |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類: | DRAM |

| 英文描述: | 64/256/512/1K/2K/4K x18 Low-Voltage Synchronous FIFOs |

| 中文描述: | 64 X 18 OTHER FIFO, 15 ns, PQFP64 |

| 封裝: | 10 X 10 MM, TQFP-64 |

| 文件頁(yè)數(shù): | 6/25頁(yè) |

| 文件大?。?/td> | 409K |

| 代理商: | CY7C4425-25ASI |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)當(dāng)前第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)

CY7C4425/4205/4215

CY7C4225/4235/4245

6

t

PAFsynch

Clock to Programmable Almost-Full Flag

(Synchronous mode, V

CC

/SMODE tied to V

SS

)

Clock to Programmable Almost-Empty Flag

[12]

(Asynchronous mode, V

CC

/SMODE tied to V

CC

)

Clock to Programmable Almost-Full Flag

(Synchronous mode, V

CC

/SMODE tied to V

SS

)

Clock to Half-Full Flag

Clock to Expansion Out

Expansion in Pulse Width

Expansion in Set-Up Time

Skew Time between Read Clock and Write

Clock for Full Flag

Skew Time between Read Clock and Write

Clock for Empty Flag

Skew Time between Read Clock and Write

Clock for Programmable Almost Empty and Pro-

grammable Almost Full Flags.

8

10

15

20

ns

t

PAEasynch

12

16

20

25

ns

t

PAEsynch

8

10

15

20

ns

t

HF

t

XO

t

XI

t

XIS

t

SKEW1

12

7

16

10

20

15

25

20

ns

ns

ns

ns

ns

3

6.5

5

6

10

10

10

14

15

12

4.5

5

t

SKEW2

5

6

10

12

ns

t

SKEW3

10

15

18

20

ns

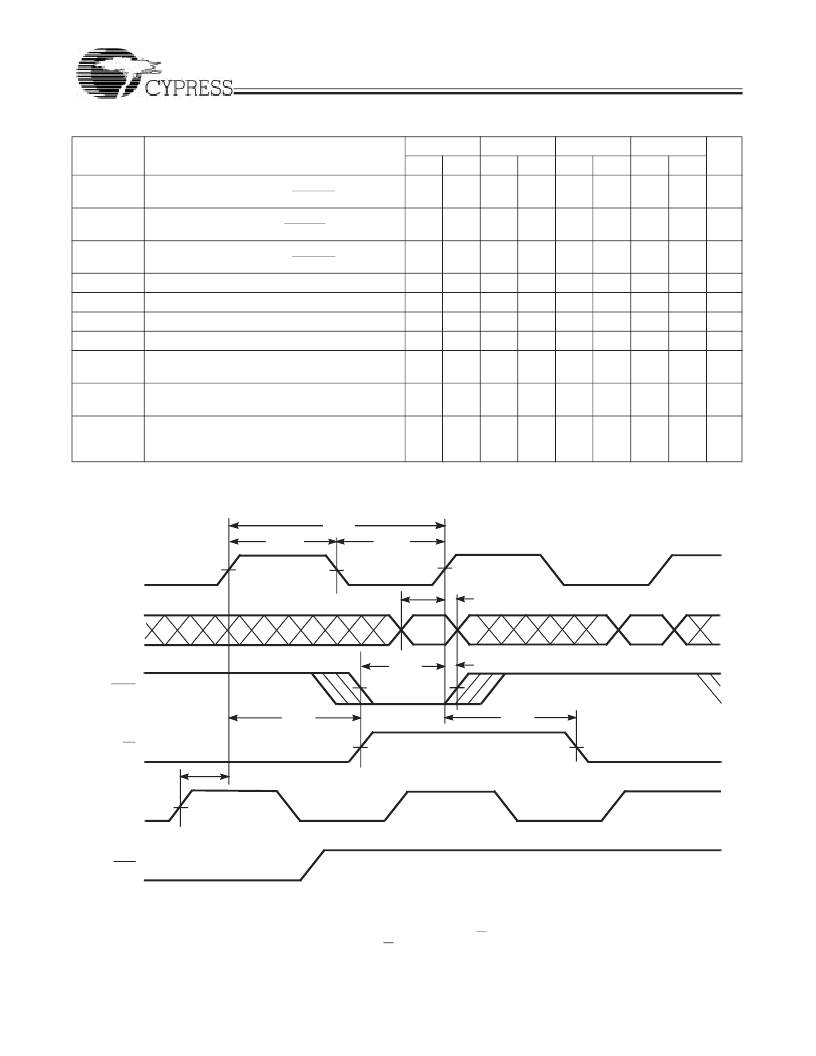

Switching Characteristics

Over the Operating Range (continued)

Parameter

Description

7C42X5-10

Min.

7C42X5-15

Min.

7C42X5-25

Min.

7C42X5-35

Min.

Max.

Max.

Max.

Max.

Unit

Switching Waveforms

Notes:

10. Pulse widths less than minimum values are not allowed.

11.

Values guaranteed by design, not currently tested.

12.

PAFasynch

, t

, after program register write will not be valid until 5 ns + t

.

13. t

is the minimum time between a rising RCLK edge and a rising WCLK edge to guarantee that FF will go HIGH during the current clock cycle. If the time between the

rising edge of RCLK and the rising edge of WCLK is less than t

SKEW1

, then FF may not change state until the next WCLK edge.

Write Cycle Timing

t

CLKH

t

CLKL

NO OPERATION

t

DS

t

SKEW1

t

ENS

WEN

t

CLK

t

DH

t

WFF

t

WFF

t

ENH

WCLK

D

0

–D

17

FF

REN

RCLK

42X5–6

[13]

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY7C4205-25ASI | 64/256/512/1K/2K/4K x18 Low-Voltage Synchronous FIFOs |

| CY7C4215-25ASI | 64/256/512/1K/2K/4K x18 Low-Voltage Synchronous FIFOs |

| CY7C4215-25AI | 64/256/512/1K/2K/4K x18 Low-Voltage Synchronous FIFOs |

| CY7C4215-25JC | 64/256/512/1K/2K/4K x18 Low-Voltage Synchronous FIFOs |

| CY7C4215-25JI | 64/256/512/1K/2K/4K x18 Low-Voltage Synchronous FIFOs |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C4425V15ASC | 制造商:Cypress Semiconductor 功能描述: |

| CY7C443-12JC | 制造商:Cypress Semiconductor 功能描述:FIFO Mem Sync Dual Width Uni-Dir 2K x 9 32-Pin PLCC |

| CY7C443-14DC | 制造商:Cypress Semiconductor 功能描述:FIFO, 2K x 9, Synchronous, 28 Pin, Ceramic, DIP |

| CY7C443-14JC | 制造商:Cypress Semiconductor 功能描述:FIFO Mem Sync Dual Width Uni-Dir 2K x 9 32-Pin PLCC |

| CY7C443-14JCT | 制造商:Cypress Semiconductor 功能描述:FIFO Mem Sync Dual Width Uni-Dir 2K x 9 32-Pin PLCC T/R |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。