- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379092 > CY7C4425-25ASC (CYPRESS SEMICONDUCTOR CORP) 64/256/512/1K/2K/4K x18 Low-Voltage Synchronous FIFOs PDF資料下載

參數(shù)資料

| 型號(hào): | CY7C4425-25ASC |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類: | DRAM |

| 英文描述: | 64/256/512/1K/2K/4K x18 Low-Voltage Synchronous FIFOs |

| 中文描述: | 64 X 18 OTHER FIFO, 15 ns, PQFP64 |

| 封裝: | 10 X 10 MM, TQFP-64 |

| 文件頁數(shù): | 7/25頁 |

| 文件大小: | 409K |

| 代理商: | CY7C4425-25ASC |

CY7C4425/4205/4215

CY7C4225/4235/4245

7

Notes:

14. .t

is the minimum time between a rising WCLK edge and a rising RCLK edge to guarantee that EF will go HIGH during the current clock cycle. It the time between the

rising edge of WCLK and the rising edge of RCLK is less than t

, then EF may not change state until the next RCLK edge.

15. The clocks (RCLK, WCLK) can be free-running during reset.

16. After reset, the outputs will be LOW if OE = 0 and three-state if OE = 1.

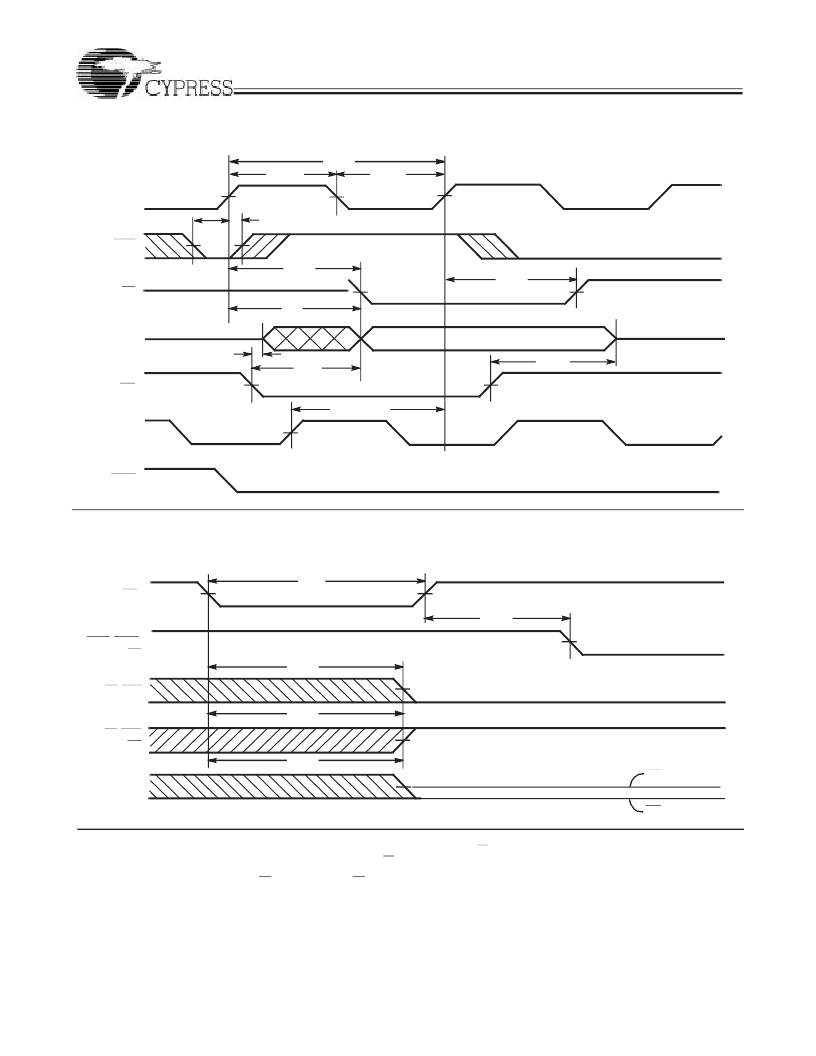

Switching Waveforms

(continued)

Read Cycle Timing

t

CLKH

t

CLKL

NO OPERATION

t

SKEW2

WEN

t

CLK

t

OHZ

t

REF

t

REF

RCLK

Q

0

–Q

17

EF

REN

WCLK

OE

t

OE

t

ENS

t

OLZ

t

A

t

ENH

VALID DATA

42X5–7

[14]

t

RS

t

RSR

Q

0 -

Q

17

RS

t

RSF

t

RSF

t

RSF

OE=1

OE=0

REN,WEN,

LD

EF,PAE

FF,PAF,

HF

42X5–8

Reset Timing

[15]

[16]

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY7C4205-25ASC | 64/256/512/1K/2K/4K x18 Low-Voltage Synchronous FIFOs |

| CY7C4215-25ASC | 64/256/512/1K/2K/4K x18 Low-Voltage Synchronous FIFOs |

| CY7C4235-25ASC | 64/256/512/1K/2K/4K x18 Low-Voltage Synchronous FIFOs |

| CY7C4245-25ASC | 64/256/512/1K/2K/4K x18 Low-Voltage Synchronous FIFOs |

| CY7C4425-25ASI | 64/256/512/1K/2K/4K x18 Low-Voltage Synchronous FIFOs |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C4425V15ASC | 制造商:Cypress Semiconductor 功能描述: |

| CY7C443-12JC | 制造商:Cypress Semiconductor 功能描述:FIFO Mem Sync Dual Width Uni-Dir 2K x 9 32-Pin PLCC |

| CY7C443-14DC | 制造商:Cypress Semiconductor 功能描述:FIFO, 2K x 9, Synchronous, 28 Pin, Ceramic, DIP |

| CY7C443-14JC | 制造商:Cypress Semiconductor 功能描述:FIFO Mem Sync Dual Width Uni-Dir 2K x 9 32-Pin PLCC |

| CY7C443-14JCT | 制造商:Cypress Semiconductor 功能描述:FIFO Mem Sync Dual Width Uni-Dir 2K x 9 32-Pin PLCC T/R |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。