- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379094 > CY7C43663 (Cypress Semiconductor Corp.) 4K x36 Unidirectional Synchronous FIFO w/ Bus Matching(4K x36 單向同步先進(jìn)先出帶總線匹配) PDF資料下載

參數(shù)資料

| 型號: | CY7C43663 |

| 廠商: | Cypress Semiconductor Corp. |

| 英文描述: | 4K x36 Unidirectional Synchronous FIFO w/ Bus Matching(4K x36 單向同步先進(jìn)先出帶總線匹配) |

| 中文描述: | 4K的x36單向同步FIFO瓦特/總線匹配(4K的x36單向同步先進(jìn)先出帶總線匹配) |

| 文件頁數(shù): | 17/28頁 |

| 文件大?。?/td> | 422K |

| 代理商: | CY7C43663 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁當(dāng)前第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁

CY7C43623

CY7C43633/CY7C43643

CY7C43663

/

CY7C43683

17

PRELIMINARY

Notes:

26. FIFO Write (CSA = LOW, W/RA = HIGH, MBA = LOW), FIFO Read (CSB = LOW, W/RB = HIGH, MBB = LOW). Data in the FIFO output register has been

read from the FIFO.

27. D = Maximum FIFO Depth = 256 for the CY7C43623, 512 for the CY7C43633, 1K for the CY7C43643, 4K for the 43663, and 16K for the CY7C43683.

28. If Port B size is word or byte, t

is referenced to the rising CLKB edge that writes the last word or byte of the long word, respectively.

29. t

is the minimum time between a rising CLKA edge and a rising CLKB edge for AF to transition HIGH in the next CLKA cycle. If the time between the

rising CLKA edge and rising CLKB edge is less than t

, then AF may transition HIGH one CLKB cycle later than shown.

30. FIFO Write (CSA = LOW, W/RA = LOW, MBA = LOW), FIFO Read (CSB = LOW, W/RB = HIGH, MBB = LOW). Data in the FIFO output register has been

read from the FIFO.

31. If Port B size is word or byte, AE is set LOW by the last word or byte read from FIFO, respectively.

32. t

is the minimum time between a rising CLKA edge and a rising CLKB edge for AE to transition HIGH in the next CLKB cycle. If the time between the

rising CLKA edge and rising CLKB edge is less than t

SKEW2

, then AE may transition HIGH one CLKB cycle later than shown.

Switching Waveforms

(continued)

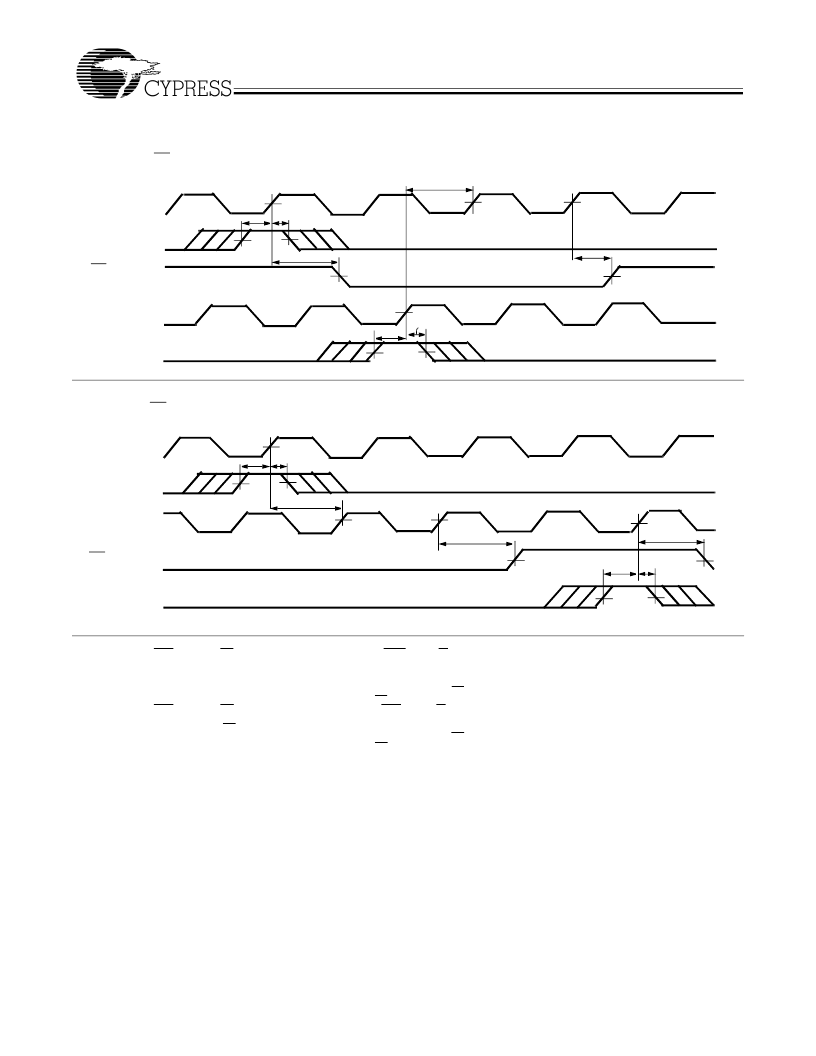

Timing for AF when FIFO is Almost Full (CY Standard and FWFT Modes)

t

PAF

t

ENH

t

ENS

t

PAF

t

ENS

t

ENH

[D

–

(Y1+1)] Words in FIFO

(D

–

Y1)Words in FIFO

t

SKEW2[29]

CLKA

ENA

AF

CLKB

ENB

[26, 27, 28]

t

PAE

t

PAE

t

ENH

t

ENS

t

SKEW2[32]

t

ENS

t

ENH

X1 Word in FIFO

(X1+1) Words in FIFO

CLKA

ENA

CLKB

AE

ENB

Timing for AE when FIFO is Almost Empty (CY Standard and FWFT Modes)

[30, 31]

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY7C43683 | 16K x36 Unidirectional Synchronous FIFO w/ Bus Matching(16K x36 單向同步先進(jìn)先出帶總線匹配) |

| CY7C43634 | 512 x36 x2 Bidirectional Synchronous FIFO w/ Bus Matching(512 x36 x2 雙向同步先進(jìn)先出 帶總線匹配) |

| CY7C43624 | 256 x36 x2 Bidirectional Synchronous FIFO w/ Bus Matching(256 x36 x2 雙向同步先進(jìn)先出帶總線匹配) |

| CY7C43644 | 1K x36 x2 Bidirectional Synchronous FIFO w/ Bus Matching(1K x36 x2 雙向同步先進(jìn)先出帶總線匹配) |

| CY7C43664 | 4K x36 x2 Bidirectional Synchronous FIFO w/ Bus Matching(4K x36 x2 雙向同步先進(jìn)先出帶總線匹配) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C43663-15AC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CY7C43664-7AC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CY7C43682-15AC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CY7C43683-10AI | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CY7C43683AV-15AC | 制造商:Cypress Semiconductor 功能描述:FIFO Mem Sync Dual Depth/Width Uni-Dir 16K x 36 128-Pin TQFP 制造商:Rochester Electronics LLC 功能描述:3.3V SYNC FIFO W/BUS MATCHING 16K X36 (NOT IDT COMPAT) - Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。