- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379090 > CY7C331 (Cypress Semiconductor Corp.) Asynchronous Registered EPLD(異步寄存式EPLD) PDF資料下載

參數(shù)資料

| 型號(hào): | CY7C331 |

| 廠商: | Cypress Semiconductor Corp. |

| 英文描述: | Asynchronous Registered EPLD(異步寄存式EPLD) |

| 中文描述: | 異步注冊(cè)可編程邏輯器件(異步寄存式可編程邏輯器件) |

| 文件頁(yè)數(shù): | 1/18頁(yè) |

| 文件大小: | 425K |

| 代理商: | CY7C331 |

當(dāng)前第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)

Asynchronous Registered EPLD

fax id: 6016

CY7C331

Cypress Semiconductor Corporation

3901 North First Street

San Jose

CA 95134

408-943-2600

January 1989 – Revised December 1992

1CY7C331

Features

Twelve I/O macrocells each having:

—One state flip-flop with an XOR sum-of-products

input

—One feedback flip-flop with input coming from the

I/O pin

—Independent (product term) set, reset, and clock in-

puts on all registers

—Asynchronous bypass capability on all registers un-

der product term control (r = s = 1)

—Global or local output enable on three-state I/O

—Feedback from either register to the array

192 product terms with variable distribution to macro-

cells

13 inputs, 12 feedback I/O pins, plus 6 shared I/O mac-

rocell feedbacks for a total of 31 true and complemen-

tary inputs

High speed: 20 ns maximum t

PD

Security bit

Space-saving 28-pin slim-line DIP package; also avail-

able in 28-pin PLCC

Low power

—90 mA typical I

CC

quiescent

—180 mA I

CC

maximum

—UV-erasable and reprogrammable

—Programming and operation 100% testable

Functional Description

The CY7C331 is the most versatile PLD available for asyn-

chronous designs. Central resources include twelve full D-type

flip-flops with separate set, reset, and clock capability. For in-

creased utility, XOR gates are provided at the D-inputs and the

product term allocation per flip-flop is variably distributed.

I/O Resources

Pins 1 through 7 and 9 through 14 serve as array inputs; pin

14 may also be used as a global output enable for the I/O

macrocell three-state outputs. Pins 15 through 20 and 23

through 28 are connected to I/O macrocells and may be man-

aged as inputs or outputs depending on the configuration and

the macrocell OE terms.

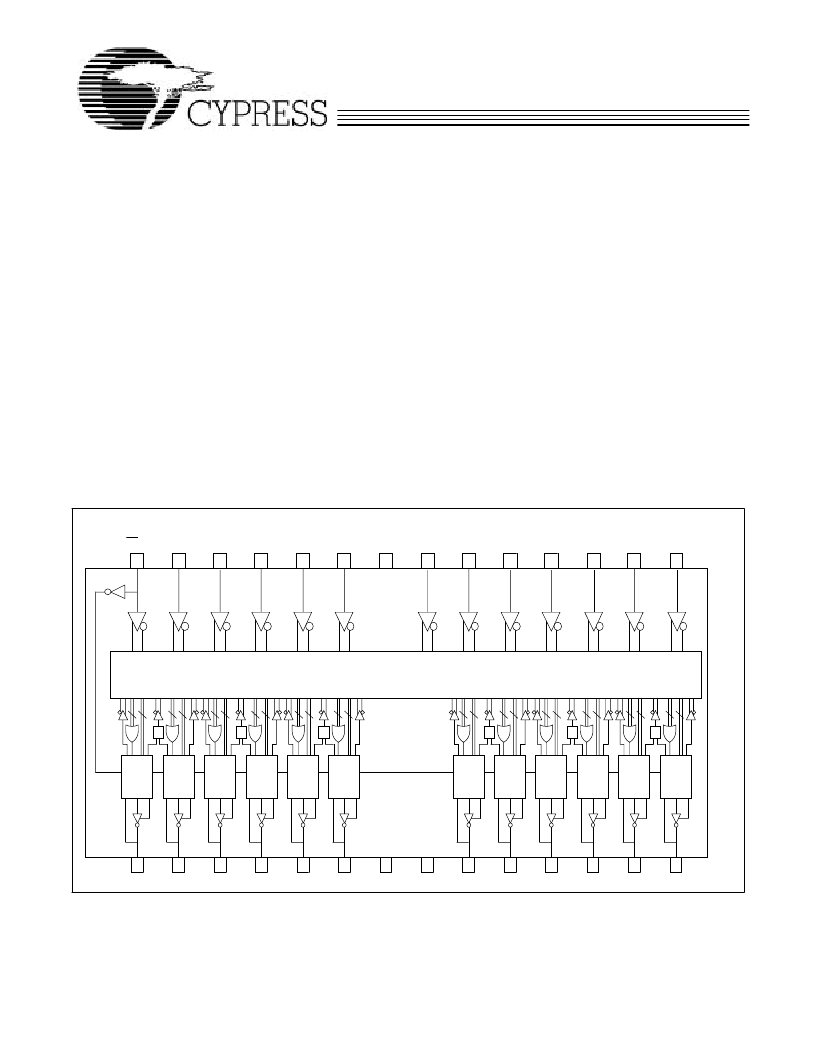

Logic Block Diagram

C331–1

14

13

12

11

10

9

7

6

5

4

3

2

1

8

15

16

17

18

19

20

23

24

25

26

27

28

22

21

GND

V

CC

PROGRAMMABLE AND ARRAY

(192x62)

10

6

8

8

12

4

6

10

4

12

8

8

I/O

11

I/O

10

I/O

9

I/O

8

I/O

7

I/O

6

I/O

5

I/O

4

I/O

3

I/O

2

I/O

1

I/O

0

GND

I

6

OE/I

12

I

11

I

10

I

9

I

8

I

7

I

5

I

4

I

3

I

2

I

1

I

0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY7C341 | 192-Macrocell MAX EPLD(192-宏單元 MAX EPLD) |

| CY7C343B | 64-Macrocell MAX EPLD(64-宏單元 MAX EPLD) |

| CY7C371-110JC | UltraLogic 32-Macrocell Flash CPLD |

| CY7C371L-66AI | UltraLogic 32-Macrocell Flash CPLD |

| CY7C371L-66JC | UltraLogic 32-Macrocell Flash CPLD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C331-25WC | 制造商:MAJOR 功能描述: 制造商:Cypress Semiconductor 功能描述:Simple EPLD, Programmable Array Logic, 28 Pin, Ceramic, DIP 制造商:CYPRESS/90'S 功能描述:Simple EPLD, Programmable Array Logic, 28 Pin, Ceramic, DIP |

| CY7C332-15JC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CY7C332-20JC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CY7C332-20PC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CY7C332-20QMB | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。