- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378497 > CY7C1165V18-300BZC (CYPRESS SEMICONDUCTOR CORP) 18-Mbit QDR⑩-II+ SRAM 4-Word Burst Architecture (2.5 Cycle Read Latency) PDF資料下載

參數(shù)資料

| 型號: | CY7C1165V18-300BZC |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類: | DRAM |

| 英文描述: | 18-Mbit QDR⑩-II+ SRAM 4-Word Burst Architecture (2.5 Cycle Read Latency) |

| 中文描述: | 512K X 36 QDR SRAM, 0.45 ns, PBGA165 |

| 封裝: | 13 X 15 MM, 1.40 MM HEIGHT, MO-216, FPBGA-165 |

| 文件頁數(shù): | 22/29頁 |

| 文件大?。?/td> | 956K |

| 代理商: | CY7C1165V18-300BZC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁當前第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁

CY7C1161V18

CY7C1176V18

CY7C1163V18

CY7C1165V18

Document Number: 001-06582 Rev. *C

Page 22 of 29

Capacitance

Tested initially and after any design or process change that may affect these parameters.

Parameter

C

IN

C

CLK

C

O

Description

Test Conditions

Max

5

6

7

Unit

pF

pF

pF

Input Capacitance

Clock Input Capacitance

Output Capacitance

T

A

= 25

°

C, f = 1 MHz,

V

DD

= 1.8V

V

DDQ

= 1.5V

Thermal Resistance

Tested initially and after any design or process change that may affect these parameters.

Parameter

Description

Test Conditions

165 FBGA

Package

17.2

Unit

Θ

JA

Thermal Resistance

(junction to ambient)

Thermal Resistance

(junction to case)

Test conditions follow standard test methods and

procedures for measuring thermal impedance, in

accordance with EIA/JESD51.

°C/W

Θ

JC

4.15

°C/W

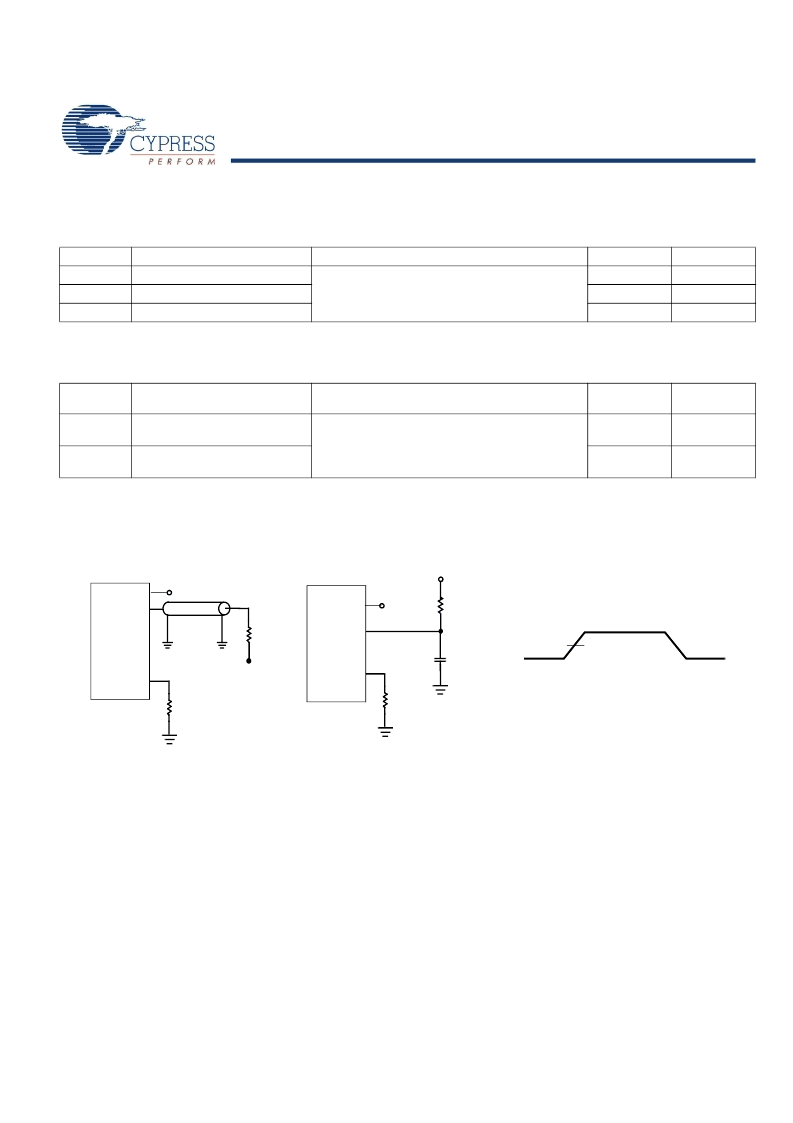

AC Test Loads and Waveforms

Figure 5. AC Test Loads and Waveforms

1.25V

0.25V

R = 50

5 pF

INCLUDING

JIG AND

SCOPE

ALL INPUT PULSES

Device

Under

Test

R

L

= 50

Z

0

= 50

V

REF

= 0.75V

V

REF

= 0.75V

[22]

0.75V

0.75V

Device

Under

Test

OUTPUT

0.75V

V

REF

V

REF

OUTPUT

ZQ

ZQ

(a)

Slew Rate = 2 V/ns

RQ =

250

(b)

RQ =

250

Notes

22.Unless otherwise noted, test conditions are based upon signal transition time of 2V/ns, timing reference levels of 0.75V, Vref = 0.75V, RQ = 250

, V

DDQ

= 1.5V, input

pulse levels of 0.25V to 1.25V, and output loading of the specified I

OL

/I

OH

and load capacitance shown in (a) of AC Test Loads.

[+] Feedback

相關PDF資料 |

PDF描述 |

|---|---|

| CY7C1165V18-300BZI | 18-Mbit QDR⑩-II+ SRAM 4-Word Burst Architecture (2.5 Cycle Read Latency) |

| CY7C1165V18-300BZXC | 18-Mbit QDR⑩-II+ SRAM 4-Word Burst Architecture (2.5 Cycle Read Latency) |

| CY7C1165V18-300BZXI | 18-Mbit QDR⑩-II+ SRAM 4-Word Burst Architecture (2.5 Cycle Read Latency) |

| CY7C1165V18-333BZC | 18-Mbit QDR⑩-II+ SRAM 4-Word Burst Architecture (2.5 Cycle Read Latency) |

| CY7C1165V18-333BZI | 18-Mbit QDR⑩-II+ SRAM 4-Word Burst Architecture (2.5 Cycle Read Latency) |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C1165V18-300BZXC | 制造商:Cypress Semiconductor 功能描述: |

| CY7C1165V18-400BZXC | 功能描述:靜態(tài)隨機存取存儲器 18M Q+, B4 2.5 LATENCY RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CY7C1165XC | 制造商:Cypress Semiconductor 功能描述: |

| CY7C11681KV18-400BZC | 功能描述:靜態(tài)隨機存取存儲器 1Mb x 18 400 MHz Sync 靜態(tài)隨機存取存儲器 RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CY7C11681KV18-400BZXC | 功能描述:靜態(tài)隨機存取存儲器 1Mb x 18 400 MHz Sync 靜態(tài)隨機存取存儲器 RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復。