- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄358697 > CY7C016AV-20JC (CYPRESS SEMICONDUCTOR CORP) 3.3V 4K/8K/16K/32K x 8/9 Dual-Port Static RAM PDF資料下載

參數(shù)資料

| 型號: | CY7C016AV-20JC |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類: | SRAM |

| 英文描述: | 3.3V 4K/8K/16K/32K x 8/9 Dual-Port Static RAM |

| 中文描述: | 16K X 9 DUAL-PORT SRAM, 20 ns, PQCC68 |

| 封裝: | PLASTIC, LCC-68 |

| 文件頁數(shù): | 1/20頁 |

| 文件大?。?/td> | 301K |

| 代理商: | CY7C016AV-20JC |

3.3V 4K/8K/16K/32K x 8/9

Dual-Port Static RAM

CY7C138AV/144AV/006AV

CY7C139AV/145AV/016AV

CY7C007AV/017AV

Cypress Semiconductor Corporation

Document #: 38-06051 Rev. *A

3901 North First Street

San Jose

CA 95134

Revised December 27, 2002

408-943-2600

25/0251

Features

True Dual-Ported memory cells which allow simulta-

neous access of the same memory location

4K/8K/16K/32K x 8 organizations

(CY7C0138AV/144AV/006AV/007AV)

4K/8K/16K/32K x 9 organizations

(CY7C0139AV/145AV/016AV/017AV)

0.35-micron CMOS for optimum speed/power

High-speed access: 20/25 ns

Low operating power

—Active: I

CC

= 115 mA (typical)

—Standby: I

SB3

= 10

μ

A (typical)

Fully asynchronous operation

Automatic power-down

Expandable data bus to 16/18 bits or more using Master/

Slave chip select when using more than one device

On-chip arbitration logic

Semaphores included to permit software handshaking

between ports

INT flag for port-to-port communication

Pin select for Master or Slave

Commercial and Industrial Temperature Ranges

Available in 68-pin PLCC (all) and 64-pin TQFP

(7C006AV & 7C144AV)

Pin-compatible and functionally equivalent to

IDT70V05, 70V06, and 70V07.

Notes:

1.

2.

3.

I/O

0

–

I/O

for x8 devices; I/O

0

–

I/O

for x9 devices.

A

–

A

for 4K devices; A

–

A

for 8K devices; A

–

A

for 16K devices; A

0

–

A

14

for 32K devices;

BUSY is an output in master mode and an input in slave mode.

I/O

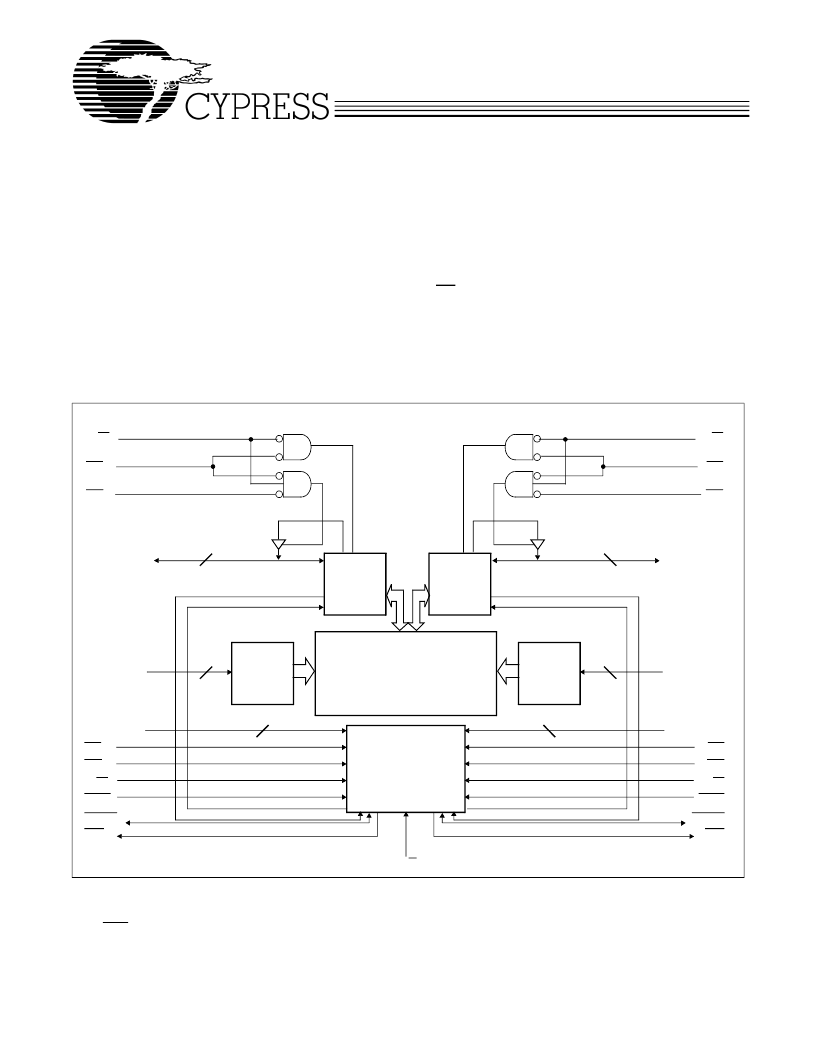

Control

Address

Decode

A

0L

–

A

11

–

14L

CE

L

OE

L

R/W

L

SEM

L

BUSY

L

INT

L

I/O

Control

Interrupt

Semaphore

Arbitration

M/S

A

0L

–

A

11

–

14L

True Dual-Ported

RAM Array

A

0R

–

A

11

–

14R

CE

R

OE

R

R/W

R

SEM

R

BUSY

R

INT

R

Address

Decode

A

0R

–

A

11

–

14R

[1]

[1]

[3]

[3]

R/W

L

OE

L

I/O

0L

–

I/O

7/8L

CE

L

R/W

R

OE

R

I/O

0R

–

I/O

7/8R

CE

R

12

–

15

8/9

12

–

15

8/9

12

–

15

12

–

15

[2]

[2]

[2]

[2]

Logic Block Diagram

For the most recent information, visit the Cypress web site at www.cypress.com

相關PDF資料 |

PDF描述 |

|---|---|

| CY7C026AV-20AC | 3.3V 4K/8K/16K x 16/18 Dual-Port Static RAM |

| CY7C1362B-166BZI | 9-Mbit (256K x 36/512K x 18) Pipelined SRAM |

| CY7C1362B-166BZC | 9-Mbit (256K x 36/512K x 18) Pipelined SRAM |

| CY7C1362B-225BZC | 9-Mbit (256K x 36/512K x 18) Pipelined SRAM |

| CY7C1362B-225BGI | BACKSHELL, MDR 68 WAY METALBACKSHELL, MDR 68 WAY METAL; Material:Aluminum; Ways, No. of:68; Colour:Steel |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C016AV-25JC | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:3.3V 4K/8K/16K/32K x 8/9 Dual-Port Static RAM |

| CY7C017A | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:32K/16K x8, 32K/16K x9 Dual-Port Static RAM |

| CY7C017A-12JC | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:32K/16K x8, 32K/16K x9 Dual-Port Static RAM |

| CY7C017A-15JC | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:32K/16K x8, 32K/16K x9 Dual-Port Static RAM |

| CY7C017A-15JI | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x9 Dual-Port SRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復。