- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379014 > CY37064P44-154JXI (CYPRESS SEMICONDUCTOR CORP) 5V, 3.3V, ISRTM High-Performance CPLDs PDF資料下載

參數(shù)資料

| 型號: | CY37064P44-154JXI |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類: | PLD |

| 英文描述: | 5V, 3.3V, ISRTM High-Performance CPLDs |

| 中文描述: | EE PLD, 7.5 ns, PQCC44 |

| 封裝: | LEAD FREE, PLASTIC, LCC-44 |

| 文件頁數(shù): | 5/64頁 |

| 文件大小: | 1798K |

| 代理商: | CY37064P44-154JXI |

第1頁第2頁第3頁第4頁當(dāng)前第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁

Ultra37000 CPLD Family

Document #: 38-03007 Rev. *D

Page 5 of 64

The buried macrocell also supports input register capability.

The buried macrocell can be configured to act as an input

register (D-type or latch) whose input comes from the I/O pin

associated with the neighboring macrocell. The output of all

buried macrocells is sent directly to the PIM regardless of its

configuration.

I/O Macrocell

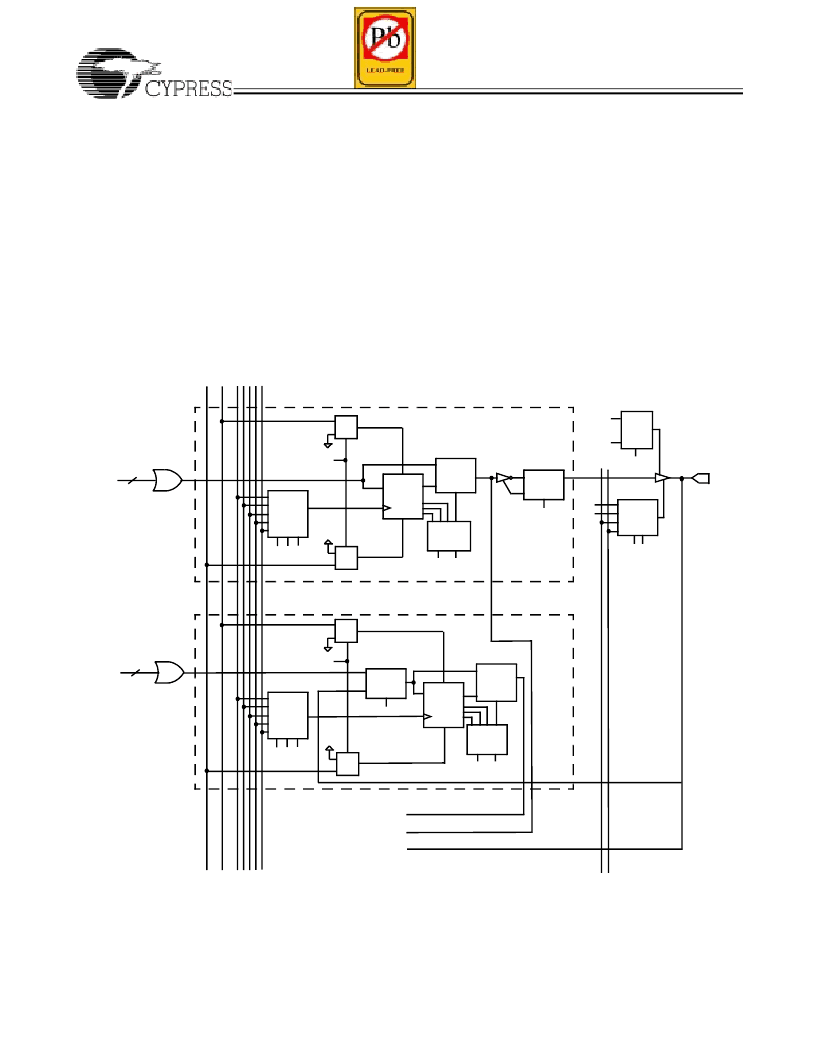

Figure 2

illustrates the architecture of the I/O macrocell. The

I/O macrocell supports the same functions as the buried

macrocell with the addition of I/O capability. At the output of the

macrocell, a polarity control mux is available to select active

LOW or active HIGH signals. This has the added advantage

of allowing significant logic reduction to occur in many appli-

cations.

The Ultra37000 macrocell features a feedback path to the PIM

separate from the I/O pin input path. This means that if the

macrocell is buried (fed back internally only), the associated

I/O pin can still be used as an input.

Bus Hold Capabilities on all I/Os

Bus-hold, which is an improved version of the popular internal

pull-up resistor, is a weak latch connected to the pin that does

not degrade the device’s performance. As a latch, bus-hold

maintains the last state of a pin when the pin is placed in a

high-impedance state, thus reducing system noise in

bus-interface applications. Bus-hold additionally allows

unused device pins to remain unconnected on the board,

which is particularly useful during prototyping as designers can

route new signals to the device without cutting trace connec-

tions to V

CC

or GND. For more information, see the application

note

Understanding Bus-Hold—A Feature of Cypress CPLDs

.

Programmable Slew Rate Control

Each output has a programmable configuration bit, which sets

the output slew rate to fast or slow. For designs concerned with

meeting FCC emissions standards the slow edge provides for

lower system noise. For designs requiring very high perfor-

mance the fast edge rate provides maximum system perfor-

mance.

C2

C3

DECODE

C2

C3

DECODE

0

1

2

3

O

C6 C5

“0”

“1”

0

1

O

D/T/L

Q

R

P

0

1

2

3

4

O

C0

0

1

O

C4

FEEDBACK TO PIM

FEEDBACK TO PIM

BLOCK RESET

ASYNCHRONOUS

0

16

TERMS

I/O MACROCELL

I/O CELL

FROM PTM

0

1

O

D/T/L

Q

R

P

FROM PTM

0

16

PRODUCT

1

O

C7

FEEDBACK TO PIM

BURIED MACROCELL

0

ASYNCHRONOUS

PRODUCT

TERMS

C1

0

1

2

3

4

Q

C24

C0 C1C24

C25

C25

4 SYNCHRONOUS CLOCKS (CLK0,CLK1,CLK2,CLK3)

1 ASYNCHRONOUS CLOCK(PTCLK)

Figure 2. I/O and Buried Macrocells

BLOCK PRESET

FAST

SLOW

C26

SLEW

0

1

0

1

0

1

0

1

OE0 OE1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY37032VP44-100JXI | 5V, 3.3V, ISRTM High-Performance CPLDs |

| CY3732VP44-200BGXC | 5V, 3.3V, ISRTM High-Performance CPLDs |

| CY3764VP44-200BGXC | Aluminum Electrolytic Radial Leaded General Purpose Capacitor; Capacitance: 22000uF; Voltage: 16V; Case Size: 22x40 mm; Packaging: Bulk |

| CY37128VP44-200BGXC | 5V, 3.3V, ISRTM High-Performance CPLDs |

| CY37256VP44-200BGXC | Aluminum Electrolytic Radial Leaded General Purpose Capacitor; Capacitance: 33uF; Voltage: 16V; Case Size: 25x50 mm; Packaging: Bulk |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY37064P44-200AC | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:5V, 3.3V, ISRTM High-Performance CPLDs |

| CY37064P44-200AXC | 制造商:Rochester Electronics LLC 功能描述: 制造商:Cypress Semiconductor 功能描述: |

| CY37064P44-200JC | 制造商:Cypress Semiconductor 功能描述:CPLD Ultra37000 Family 2K Gates 64 Macro Cells 200MHz 5V 44-Pin PLCC |

| CY37064P44-200JXC | 制造商:Rochester Electronics LLC 功能描述: 制造商:Cypress Semiconductor 功能描述: |

| CY37064P84-125JC | 功能描述:IC CPLD 64 MACROCELL 84-PLCC RoHS:否 類別:集成電路 (IC) >> 嵌入式 - CPLD(復(fù)雜可編程邏輯器件) 系列:Ultra37000™ 標(biāo)準(zhǔn)包裝:40 系列:ispMACH® 4000C 可編程類型:系統(tǒng)內(nèi)可編程 最大延遲時間 tpd(1):5.0ns 電壓電源 - 內(nèi)部:1.65 V ~ 1.95 V 邏輯元件/邏輯塊數(shù)目:32 宏單元數(shù):512 門數(shù):- 輸入/輸出數(shù):128 工作溫度:-40°C ~ 105°C 安裝類型:表面貼裝 封裝/外殼:176-LQFP 供應(yīng)商設(shè)備封裝:176-TQFP(24x24) 包裝:托盤 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。