- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378482 > CY28326OCT (CYPRESS SEMICONDUCTOR CORP) FTG for VIA PT880 Serial Chipset PDF資料下載

參數(shù)資料

| 型號(hào): | CY28326OCT |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類: | XO, clock |

| 英文描述: | FTG for VIA PT880 Serial Chipset |

| 中文描述: | 333.3 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 封裝: | SSOP-48 |

| 文件頁數(shù): | 3/23頁 |

| 文件大小: | 288K |

| 代理商: | CY28326OCT |

CY28326

Document #: 38-07616 Rev. *A

Page 3 of 23

24

VDD48

AGP0/AGP2

*RatioSEL

/AGP1

I

Power for 48MHz clock output.

AGP Clock Output.

Power-on Bi-directional Input/output.

At power up, RatioSel is

the input. when the power supply voltage crosses the input

threshold voltage, RatioSel state is latched and this pin becomes

AGP clock output. Default pull-up.

3.3V power supply for AGP clock output.

Ground for AGP clock output.

System Reset Control Output.

Serial clock input.

Conforms to the Philips I

2

C specification.

Serial clock input.

Conforms to the Philips I

2

C specification of a

Slave Receive/Transmit device. it is an input when receiving data.

It is open drain output when acknowledging or transmitting data.

VTT_PWRGD: 3.3V LVTTL input to determine when FS[D:A],

MODE, RatioSEL and 24_48_SEL inputs are valid and ready to

be sampled.

PD#: Invokes powerdown mode. Default Internal pull up.

Power for 25 MHz clock output. 3.3V Power Supply.

25 MHz Clock Output.

Ground for 25 MHz clock output.

CPU Clock outputs.

Power for CPU clock output.

Ground for CPU clock output.

Current Reference.

A precision resistor is attached to this pin,

which is connected to the internal current reference.

Ground for output.

3.3V Power Supply for output

25,29

26

VDDAGP

VDDAGP

O

I/O

27

28

30

31

32

VDDAGP

VSSAGP

SRESET#

SCLK

SDATA

I

I

O

I

I/O

33

*VTT_PWRG

D/PD#

I

34

VDDSRC

25MHz[0:1]

VSSSRC

I

35,36

37

VDDSRC

O

I

O

I

I

I

39,38,42,41,45,44 CPU[T/C][0:2] VDDCPU

40

VDDCPU

43

VSSCPU

46

IREF

47

48

VSSA

VDDA

I

I

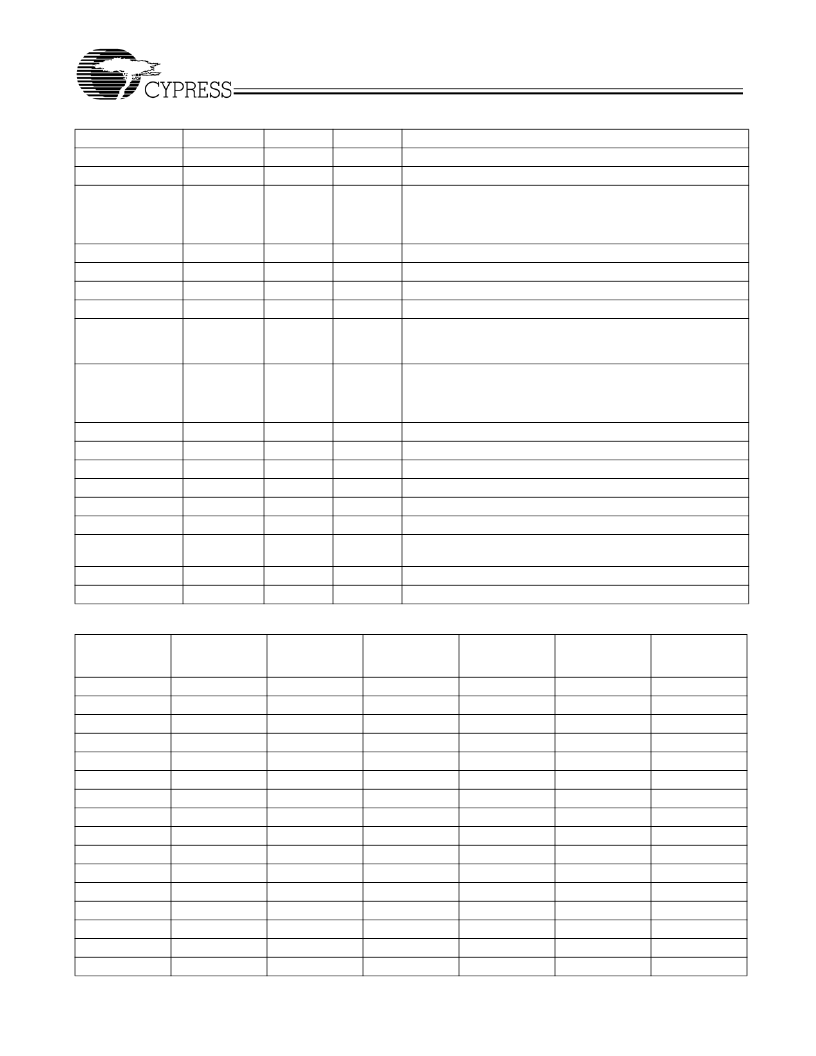

Table 1. Frequency Table

FS(D:A)

FS(3:0)

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

1111

CPU (MHz)

110.0

146.6

220.0

183.3

233.3

266.6

333.3

300.0

100.9

133.9

200.9

166.9

100.0

133.3

200.0

166.6

AGP (MHz)

73.3

73.3

73.3

73.3

66.7

66.7

66.7

66.7

67.3

67.0

67.0

66.8

66.7

66.7

66.7

66.7

PCI (MHz)

36.6

36.6

36.6

36.6

33.3

33.3

33.3

33.3

33.6

33.5

33.5

33.4

33.3

33.3

33.3

33.3

SATA (MHz)

25.0

25.0

25.0

25.0

25.0

25.0

25.0

25.0

25.0

25.0

25.0

25.0

25.0

25.0

25.0

25.0

VCO (MHz)

660.00

586.68

440.00

733.33

466.67

533.33

666.67

600.00

807.2

803.4

803.6

667.6

800.00

800.00

800.00

666.67

PLL Gear

Constant

(Million)

25.00258122

37.50387182

75.00774365

37.50387182

75.00774365

75.00774365

75.00774365

75.00774365

18.75193591

25.00258122

37.50387182

37.50387182

18.75193591

25.00258122

37.50387182

37.50387182

Pin Definition

(continued)

Pin No.

Name

PWR

Type

Description

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY28326OXC | Single Pole Normally Open: 1-Form-A |

| CY28326OXCT | Single Pole Normally Open: 1-Form-A |

| CY28341-2 | Universal Clock Chip for VIA P4M/KT/KM400 DDR Systems |

| CY29962 | 2.5V/3.3V, 150-MHz Multi-Output Zero Delay Buffer |

| CY30 | Sensor interface for an inductive engine wheel speed single rotation sensor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY28326OXC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CY28326OXCT | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:FTG for VIA PT880 Serial Chipset |

| CY28326SPC | 制造商:Cypress Semiconductor 功能描述: |

| CY28329 | 制造商:SPECTRALINEAR 制造商全稱:SPECTRALINEAR 功能描述:133 MHz Spread Spectrum Clock Synthesizer/Driver with Differential CPU Outputs |

| CY28329OXC | 功能描述:時(shí)鐘驅(qū)動(dòng)器及分配 Intel CK-408B for Plumas chipset RoHS:否 制造商:Micrel 乘法/除法因子:1:4 輸出類型:Differential 最大輸出頻率:4.2 GHz 電源電壓-最大: 電源電壓-最小:5 V 最大工作溫度:+ 85 C 封裝 / 箱體:SOIC-8 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。