- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379001 > CY2292SL-XXX (CYPRESS SEMICONDUCTOR CORP) Three-PLL General-Purpose EPROM Programmable Clock Generator PDF資料下載

參數(shù)資料

| 型號(hào): | CY2292SL-XXX |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類: | XO, clock |

| 英文描述: | Three-PLL General-Purpose EPROM Programmable Clock Generator |

| 中文描述: | 80 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO16 |

| 封裝: | 0.150 INCH, MS-012, SOIC-16 |

| 文件頁數(shù): | 2/11頁 |

| 文件大小: | 189K |

| 代理商: | CY2292SL-XXX |

CY2292

Document #: 38-07449 Rev. *B

Page 2 of 11

Operation

The CY2292 is a third-generation family of clock generators.

The CY2292 is upwardly compatible with the industry standard

ICD2023 and ICD2028 and continues their tradition by

providing a high level of customizable features to meet the

diverse clock generation needs of modern motherboards and

other synchronous systems.

All parts provide a highly configurable set of clocks for PC

motherboard applications. Each of the four configurable clock

outputs (CLKA–CLKD) can be assigned 1 of 30 frequencies in

any combination. Multiple outputs configured for the same or

related

[3]

frequencies will have low (

≤

500 ps) skew, in effect

providing on-chip buffering for heavily loaded signals.

The CY2292 can be configured for either 5V or 3.3V operation.

The internal ROM tables use EPROM technology, allowing full

customization of output frequencies. The reference oscillator

has been designed for 10-MHz to 25-MHz crystals, providing

additional flexibility. No external components are required with

this crystal. Alternatively, an external reference clock of

frequency between 1 MHz and 30 MHz can be used.

Output Configuration

The CY2292 has four independent frequency sources on-chip.

These are the reference oscillator, and three Phase-Locked

Loops (PLLs). Each PLL has a specific function. The System

PLL (SPLL) provides fixed output frequencies on the config-

urable outputs. The SPLL offers the most output frequency

divider options. The CPU PLL (CPLL) is controlled by the

select inputs (S0–S2) to provide eight user-selectable

frequencies with smooth slewing between frequencies. The

Utility PLL (UPLL) provides the most accurate clock. It is often

used for miscellaneous frequencies not provided by the other

frequency sources.

All configurations are EPROM programmable, providing short

sample and production lead times. Please refer to the appli-

cation note

Understanding the CY2291, CY2292, and CY2295

for information on configuring the part.

Notes:

1. For best accuracy, use a parallel-resonant crystal, C

≈

17 pF or 18 pF.

2. Float XTALOUT pin if XTALIN is driven by reference clock (as opposed to crystal).

3. Please refer to application note “Understanding the CY2291, CY2292 and CY2295” for more information.

4. The CY2292 has weak pull-downs on all outputs. Hence, when a three-state condition is forced on the outputs, the output pins are pulled LOW.

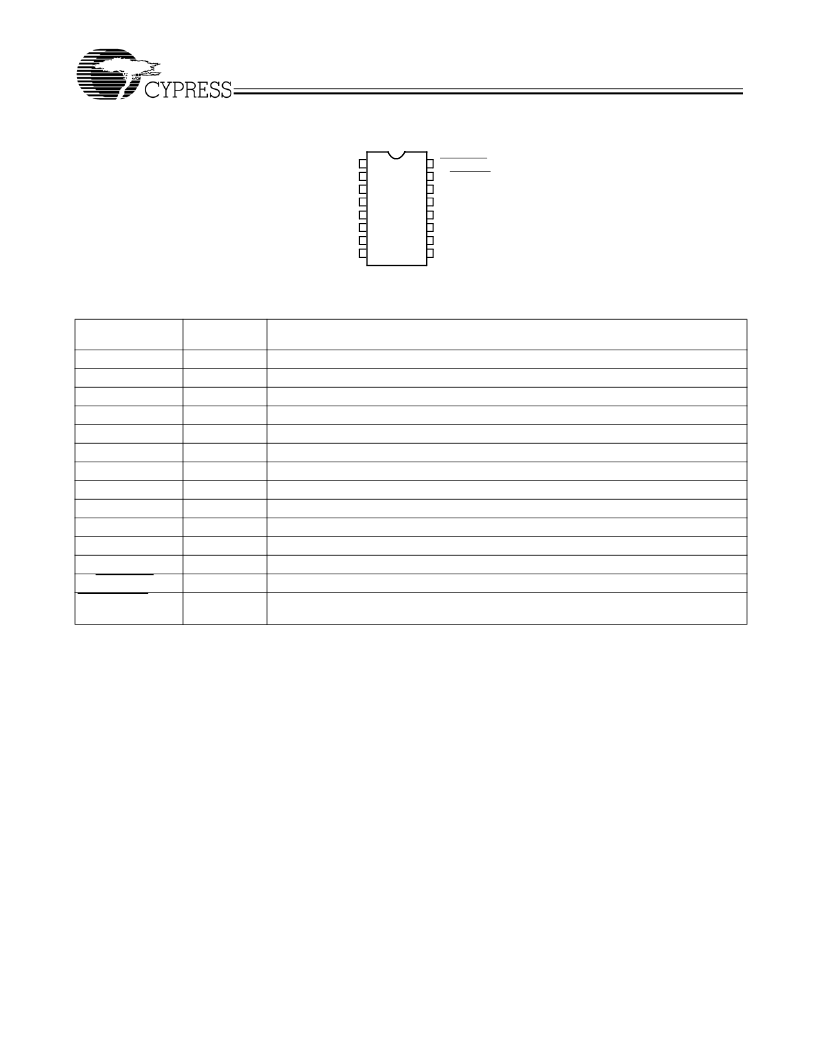

Pin Summary

Name

Pin Number

CY2292

1

2, 14

3, 11

4

5

6

7

8

9

10

12

13

15

16

Description

CLKC

V

DD

GND

XTALIN

[1]

XTALOUT

[1, 2]

XBUF

CLKD

CPUCLK

CLKB

CLKA

S0

S1

S2/SUSPEND

SHUTDOWN/OE

Configurable clock output C.

Voltage supply.

Ground.

Reference crystal input or external reference clock input.

Reference crystal feedback.

Buffered reference clock output.

Configurable clock output D.

CPU frequency clock output.

Configurable clock output B.

Configurable clock output A.

CPU clock select input, bit 0.

CPU clock select input, bit 1.

CPU clock select input, bit 2. Optionally enables suspend feature when LOW.

[3]

Places outputs in three-state

[4]

condition and shuts down chip when LOW. Optionally, only

places outputs in three-state

[4]

condition and does not shut down chip when LOW.

1

2

3

4

5

6

7

8

9

10

CLKC

VDD

GND

XTALIN

XTALOUT

XBUF

CLKD

CPUCLK

SHUTDOWN/OE

S2/SUSPEND

VDD

S1

S0

GND

CLKA

CLKB

16-pin SOIC

11

12

13

14

15

16

CY2292

Pin Configurations

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY2292SL-XXXT | Three-PLL General-Purpose EPROM Programmable Clock Generator |

| CY2292FZXT | Three-PLL General-Purpose EPROM Programmable Clock Generator |

| CY2292FT | Three-PLL General-Purpose EPROM Programmable Clock Generator |

| CY2292FZ | Three-PLL General-Purpose EPROM Programmable Clock Generator |

| CY2292FZT | Three-PLL General-Purpose EPROM Programmable Clock Generator |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY2292SL-XXXT | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:Three-PLL General-Purpose EPROM Programmable Clock Generator |

| CY2292SXC-492 | 功能描述:時(shí)鐘發(fā)生器及支持產(chǎn)品 3PLL GenPurpose EPRM Program Clock Gen RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

| CY2292SXC-492T | 功能描述:時(shí)鐘發(fā)生器及支持產(chǎn)品 3PLL GenPurpose EPRM Program Clock Gen RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

| CY2292SXC-984 | 功能描述:時(shí)鐘發(fā)生器及支持產(chǎn)品 3PLL GenPurpose EPRM Program Clock Gen RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

| CY2292SXC-984T | 功能描述:時(shí)鐘發(fā)生器及支持產(chǎn)品 3PLL GenPurpose EPRM Program Clock Gen RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。