- 您現在的位置:買賣IC網 > PDF目錄378996 > CY14B104L-ZS15XIT (CYPRESS SEMICONDUCTOR CORP) 4-Mbit (512K x 8/256K x 16) nvSRAM PDF資料下載

參數資料

| 型號: | CY14B104L-ZS15XIT |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類: | DRAM |

| 英文描述: | 4-Mbit (512K x 8/256K x 16) nvSRAM |

| 中文描述: | 512K X 8 NON-VOLATILE SRAM, 15 ns, PDSO44 |

| 封裝: | ROHS COMPLIANT, TSOP2-44 |

| 文件頁數: | 10/21頁 |

| 文件大?。?/td> | 371K |

| 代理商: | CY14B104L-ZS15XIT |

CY14B104L/CY14B104N

PRELIMINARY

Document #: 001-07102 Rev. *E

Page 10 of 21

AC Test Conditions

Input Pulse Levels ................................................... 0V to 3V

Input Rise and Fall Times (10% - 90%) ....................... <5 ns

Input and Output Timing Reference Levels ....................1.5V

Notes

8. WE must be HIGH during SRAM read cycles.

9. Device is continuously selected with CE and OE both LOW.

10.Measured ±200 mV from steady state output voltage.

11. If WE is LOW when CE goes LOW, the outputs remain in the high impedance state.

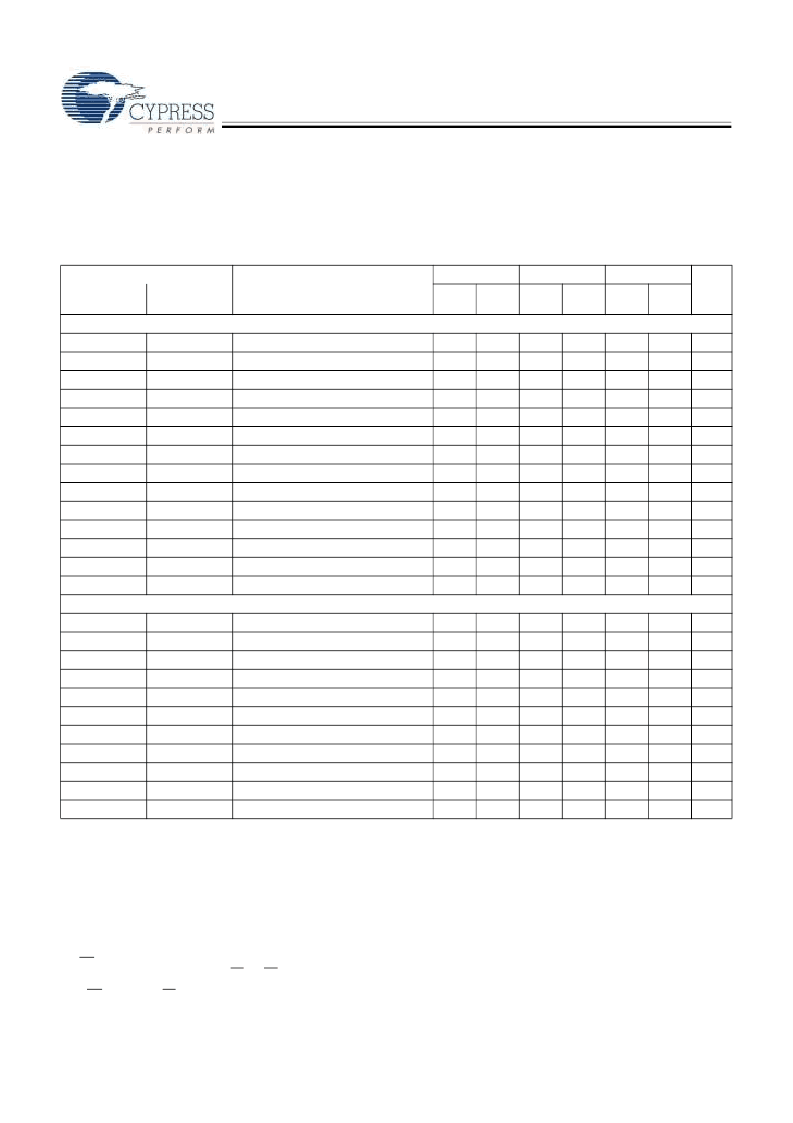

AC Switching Characteristics

Parameters

Description

15ns

25ns

45ns

Unit

Cypress

Parameters

SRAM Read Cycle

t

ACE

t

RC[8]

t

AA[9]

t

DOE

t

OHA

t

LZCE[10]

t

HZCE[10]

t

LZOE[10]

t

HZOE[10]

t

PU[7]

t

PD[7]

t

DBE

t

LZBE

t

HZBE

SRAM Write Cycle

t

WC

t

PWE

t

SCE

t

SD

t

HD

t

AW

t

SA

t

HA

t

HZWE[10,11]

t

LZWE[10]

t

BW

Alt.

Parameters

Min

Max

Min

Max

Min.

Max.

t

ACS

t

RC

t

AA

t

OE

t

OH

t

LZ

t

HZ

t

OLZ

t

OHZ

t

PA

t

PS

-

-

-

Chip Enable Access Time

Read Cycle Time

Address Access Time

Output Enable to Data Valid

Output Hold After Address Change

Chip Enable to Output Active

Chip Disable to Output Inactive

Output Enable to Output Active

Output Disable to Output Inactive

Chip Enable to Power Active

Chip Disable to Power Standby

Byte Enale to Data Valid

Byte Enable to Output Active

Byte Disable to Output Inactive

15

25

45

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

15

25

45

15

10

25

12

45

20

3

3

3

3

3

3

7

10

15

0

0

0

7

10

15

0

0

0

15

10

25

12

45

22

0

0

0

7

10

22

t

WC

t

WP

t

CW

t

DW

t

DH

t

AW

t

AS

t

WR

t

WZ

t

OW

-

Write Cycle Time

Write Pulse Width

Chip Enable To End of Write

Data Setup to End of Write

Data Hold After End of Write

Address Setup to End of Write

Address Setup to Start of Write

Address Hold After End of Write

Write Enable to Output Disable

Output Active after End of Write

Byte Enable to End of Write

15

10

15

5

0

15

0

0

25

20

20

10

0

20

0

0

45

30

30

15

0

30

0

0

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

7

10

15

3

3

3

15

20

30

[+] Feedback

相關PDF資料 |

PDF描述 |

|---|---|

| CY14B104L-ZS25XCT | 4-Mbit (512K x 8/256K x 16) nvSRAM |

| CY14B104L-ZS25XI | 4-Mbit (512K x 8/256K x 16) nvSRAM |

| CY14B104L-ZS25XIT | 4-Mbit (512K x 8/256K x 16) nvSRAM |

| CY14B104L-ZS45XCT | 4-Mbit (512K x 8/256K x 16) nvSRAM |

| CY14B104L-ZS45XI | 4-Mbit (512K x 8/256K x 16) nvSRAM |

相關代理商/技術參數 |

參數描述 |

|---|---|

| CY14B104L-ZS20XC | 功能描述:NVRAM 512Kb x 8, 2.7-3.6V 20ns nvSRAM RoHS:否 制造商:Maxim Integrated 數據總線寬度:8 bit 存儲容量:1024 Kbit 組織:128 K x 8 接口類型:Parallel 訪問時間:70 ns 電源電壓-最大:5.5 V 電源電壓-最小:4.5 V 工作電流:85 mA 最大工作溫度:+ 70 C 最小工作溫度:0 C 封裝 / 箱體:EDIP 封裝:Tube |

| CY14B104L-ZS20XCT | 功能描述:NVRAM 4 Mbit (512K x 8) 20ns nvSRAM RoHS:否 制造商:Maxim Integrated 數據總線寬度:8 bit 存儲容量:1024 Kbit 組織:128 K x 8 接口類型:Parallel 訪問時間:70 ns 電源電壓-最大:5.5 V 電源電壓-最小:4.5 V 工作電流:85 mA 最大工作溫度:+ 70 C 最小工作溫度:0 C 封裝 / 箱體:EDIP 封裝:Tube |

| CY14B104L-ZS20XI | 功能描述:NVRAM 4 Mbit (512K x 8) 20ns nvSRAM RoHS:否 制造商:Maxim Integrated 數據總線寬度:8 bit 存儲容量:1024 Kbit 組織:128 K x 8 接口類型:Parallel 訪問時間:70 ns 電源電壓-最大:5.5 V 電源電壓-最小:4.5 V 工作電流:85 mA 最大工作溫度:+ 70 C 最小工作溫度:0 C 封裝 / 箱體:EDIP 封裝:Tube |

| CY14B104L-ZS20XIT | 功能描述:NVRAM 4 Mbit (512K x 8) 20ns nvSRAM RoHS:否 制造商:Maxim Integrated 數據總線寬度:8 bit 存儲容量:1024 Kbit 組織:128 K x 8 接口類型:Parallel 訪問時間:70 ns 電源電壓-最大:5.5 V 電源電壓-最小:4.5 V 工作電流:85 mA 最大工作溫度:+ 70 C 最小工作溫度:0 C 封裝 / 箱體:EDIP 封裝:Tube |

| CY14B104L-ZS25XC | 功能描述:NVRAM 4 Mbit (512K x 8) 25ns nvSRAM RoHS:否 制造商:Maxim Integrated 數據總線寬度:8 bit 存儲容量:1024 Kbit 組織:128 K x 8 接口類型:Parallel 訪問時間:70 ns 電源電壓-最大:5.5 V 電源電壓-最小:4.5 V 工作電流:85 mA 最大工作溫度:+ 70 C 最小工作溫度:0 C 封裝 / 箱體:EDIP 封裝:Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復。