- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄3768 > CS82C55A96 (Intersil)IC I/O EXPANDER 24B 44PLCC PDF資料下載

參數(shù)資料

| 型號: | CS82C55A96 |

| 廠商: | Intersil |

| 文件頁數(shù): | 15/29頁 |

| 文件大小: | 0K |

| 描述: | IC I/O EXPANDER 24B 44PLCC |

| 標準包裝: | 500 |

| 接口: | 可編程 |

| 輸入/輸出數(shù): | 24 |

| 中斷輸出: | 無 |

| 電源電壓: | 4.5 V ~ 5.5 V |

| 工作溫度: | 0°C ~ 70°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 44-LCC(J 形引線) |

| 供應商設備封裝: | 44-PLCC |

| 包裝: | 管件 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁當前第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁

22

FN2969.10

November 16, 2006

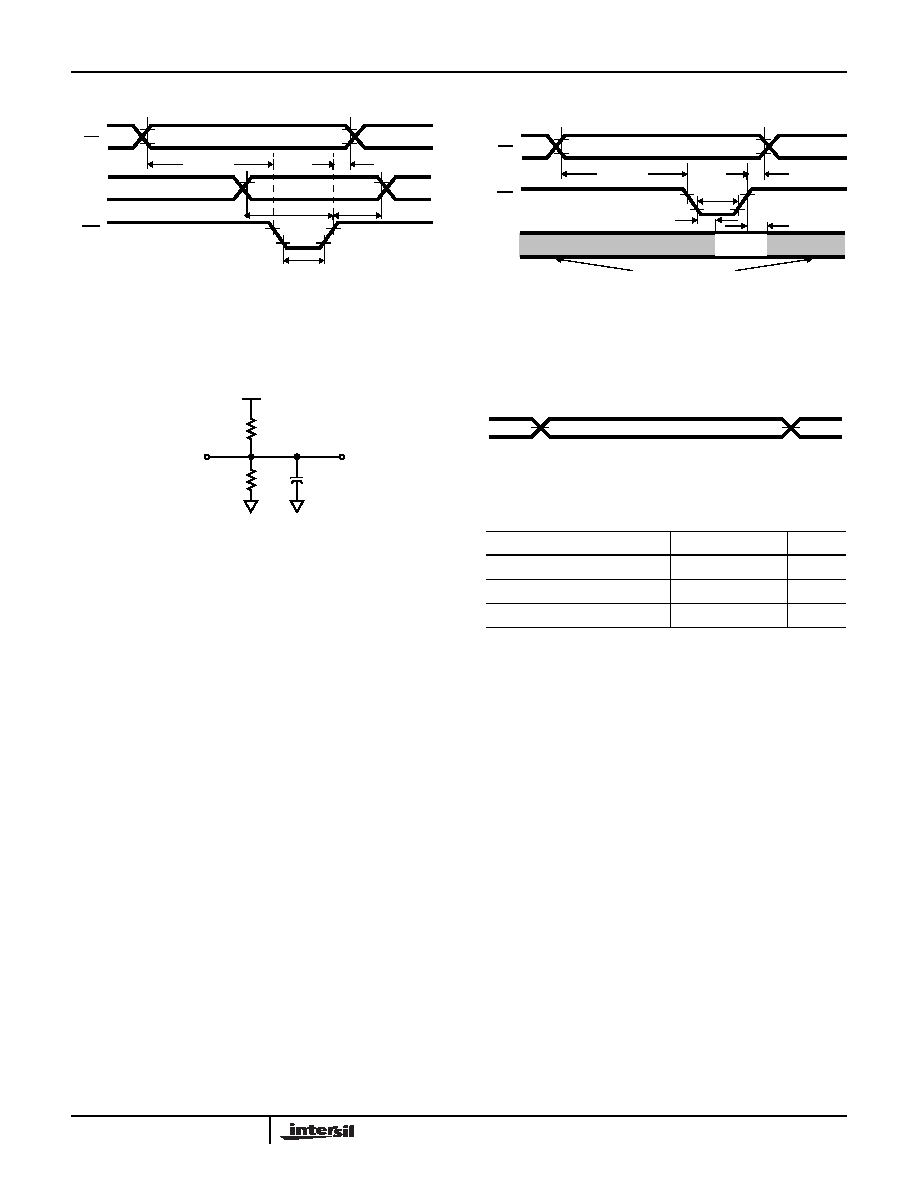

FIGURE 30. WRITE TIMING

FIGURE 31. READ TIMING

Timing Waveforms (Continued)

WR

DATA

A0-A1,

CS

BUS

tWW (9)

tDW (10)

tWD (11)

tWA (8)

tAW (7)

RD

DATA

A0-A1,

CS

BUS

tRR (3)

tRA (2)

tAR (1)

VALID

(4) tRD

tDF (5)

HIGH IMPEDANCE

AC Test Circuit

AC Testing Input, Output Waveforms

R1

V1

OUTPUT FROM

DEVICE UNDER

TEST

POINT

C1

R2

(SEE NOTE)

INPUT

VIH + 0.4V

VIL - 0.4V

1.5V

VOH

VOL

OUTPUT

AC Testing: All AC Parameters tested as per test circuits. Input RISE

and FALL times are driven at 1ns/V.

TEST CONDITION DEFINITION TABLE

TEST CONDITION

V1

R1

R2

C1

1

1.7V

523

Ω

Open

150pF

2VCC

2k

Ω

1.7k

Ω

50pF

3

1.5V

750

Ω

Open

50pF

82C55A

NOTE: Includes STRAY and JIG Capacitance

相關PDF資料 |

PDF描述 |

|---|---|

| IS82C55A-5Z96 | IC I/O EXPANDER 24B 44PLCC |

| ATMEGA8535-16AUR | MCU AVR 8K FLASH 16MHZ 44TQFP |

| IS82C55A-5Z | IC I/O EXPANDER 24B 44PLCC |

| CS82C55A-596 | IC I/O EXPANDER 24B 44PLCC |

| CS82C55A-5 | IC I/O EXPANDER 24B 44PLCC |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| CS82C55A96S2580 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CS82C55A96S5001 | 制造商:Intersil Corporation 功能描述: |

| CS82C55AR2490 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CS82C55AS2507 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CS82C55AZ | 功能描述:外圍驅(qū)動器與原件 - PCI PERI PRG-I/O 5V 8MHZ 44PLCC COM RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復。