- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄352815 > CL10K50SFC256-3 FPGA PDF資料下載

參數(shù)資料

| 型號: | CL10K50SFC256-3 |

| 英文描述: | FPGA |

| 中文描述: | FPGA的 |

| 文件頁數(shù): | 3/16頁 |

| 文件大小: | 178K |

| 代理商: | CL10K50SFC256-3 |

LIBERATOR CL10K30A

Page 11

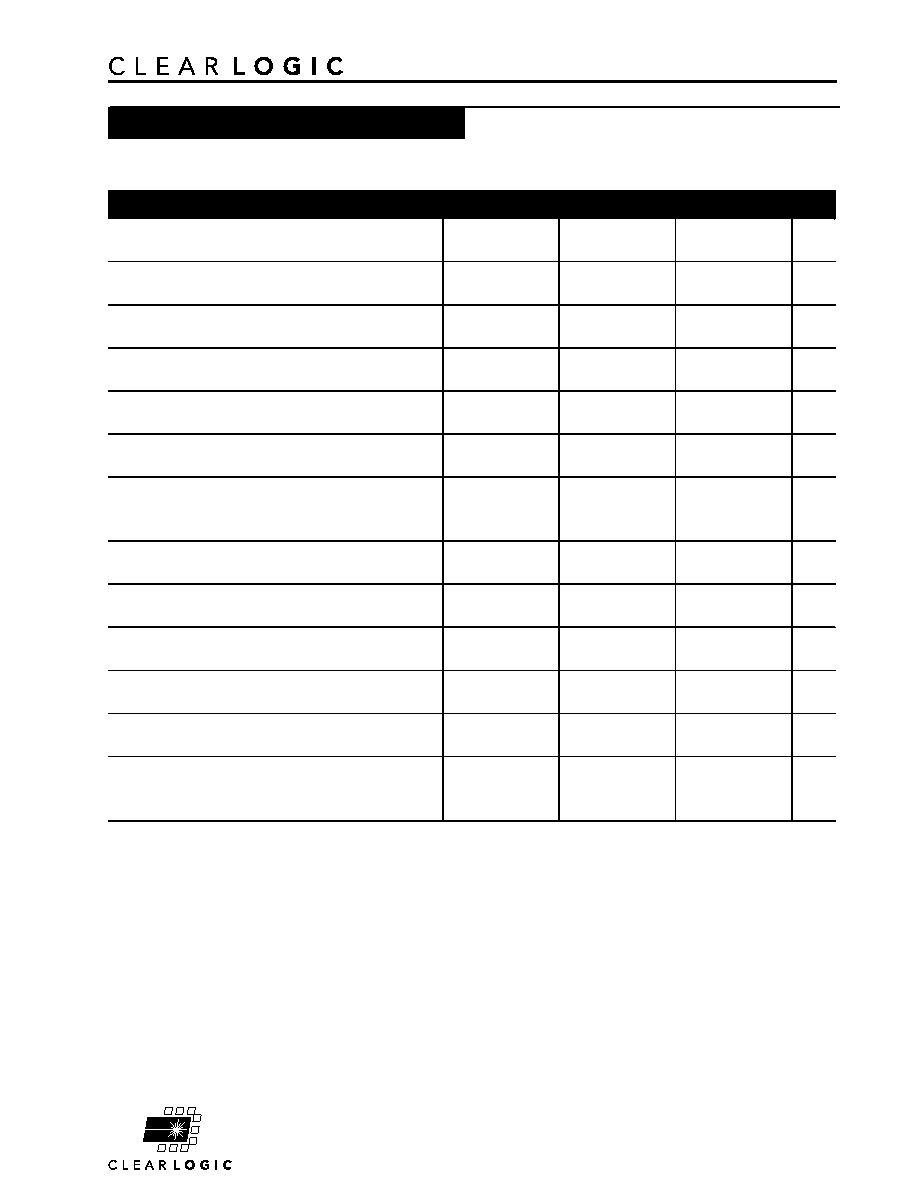

AC Electrical Specifications cont.

Symbol

Parameter

Min

Max

Min

Max

Min

Max Unit

tDIN2IOE

Delay from Dedicated Input Pin to IOE

Control Input

3.9

4.4

5.1

ns

tDIN2LE

Delay from Dedicated Input Pin to LE or EAB

Control Input

1.2

1.5

1.9

ns

tDIN2DATA

Delay from Dedicated Input or Clock Pin to

LE or EAB Data

3.2

3.6

4.5

ns

tDCLK2IOE Delay from Dedicated Clock Pin to IOE Clock

3.0

3.5

4.6

ns

tDCLK2LE

Delay from Dedicated Clock Pin to LE or EAB

Clock

1.2

1.5

1.9

ns

tSAMELAB Delay from an LE to LE in Same LAB

0.1

0.2

ns

tSAMEROW

Delay for Driving a Row IOE, LE or EAB to a

Row IOE, LE or EAB in the Same Row

2.3

2.4

2.7

ns

tSAMECOLUMN

Delay from an LE to IOE in the Same

Column

1.3

1.4

1.9

ns

tDIFFROW

Delay for Driving a Column IOE, LE or EAB to

an LE or EAB in a Different Row

3.6

3.8

4.6

ns

tTWOROWS

Delay for Driving a Row IOE or EAB to an LE

or EAB in a Different Row

5.9

6.2

7.3

ns

tLEPERIPH

Delay from an LE to IOE Control Signal via

the Peripheral Dontol Bus

3.5

3.8

4.1

ns

tLABCARRY

Delay from an LE Carry-out Signal to an LE

Carry-in Signal in a Different LAB

0.3

0.4

0.5

ns

tLABCASC

Delay from an LE Cascade-out Signal to an

LE Cascade-in Signal in a Different LAB

0.9

1.1

1.4

ns

Speed: -1

Speed: -2

Speed: -3

10KA tbl 09C

Interconnect Timing Parameters[5]

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CL10K50SFC256-4 | FPGA |

| CL10K50SQC208-1 | FPGA |

| CL10K50SQC208-1X | FPGA |

| CL10K50SQC208-2 | FPGA |

| CL10K50SQC208-2X | FPGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CL10K50SFC256-4 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FPGA |

| CL10K50SQC208-1 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FPGA |

| CL10K50SQC208-1X | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FPGA |

| CL10K50SQC208-2 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FPGA |

| CL10K50SQC208-2X | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FPGA |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。