- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378446 > CH7013A-V (Electronic Theatre Controls, Inc.) Digital PC to TV Encoder PDF資料下載

參數(shù)資料

| 型號: | CH7013A-V |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | Digital PC to TV Encoder |

| 中文描述: | 數(shù)碼電腦電視編碼器 |

| 文件頁數(shù): | 25/46頁 |

| 文件大?。?/td> | 249K |

| 代理商: | CH7013A-V |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁當(dāng)前第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁

CHRONTEL

CH7013A

201-0000-041 Rev. 1.0, 6/14/2000

25

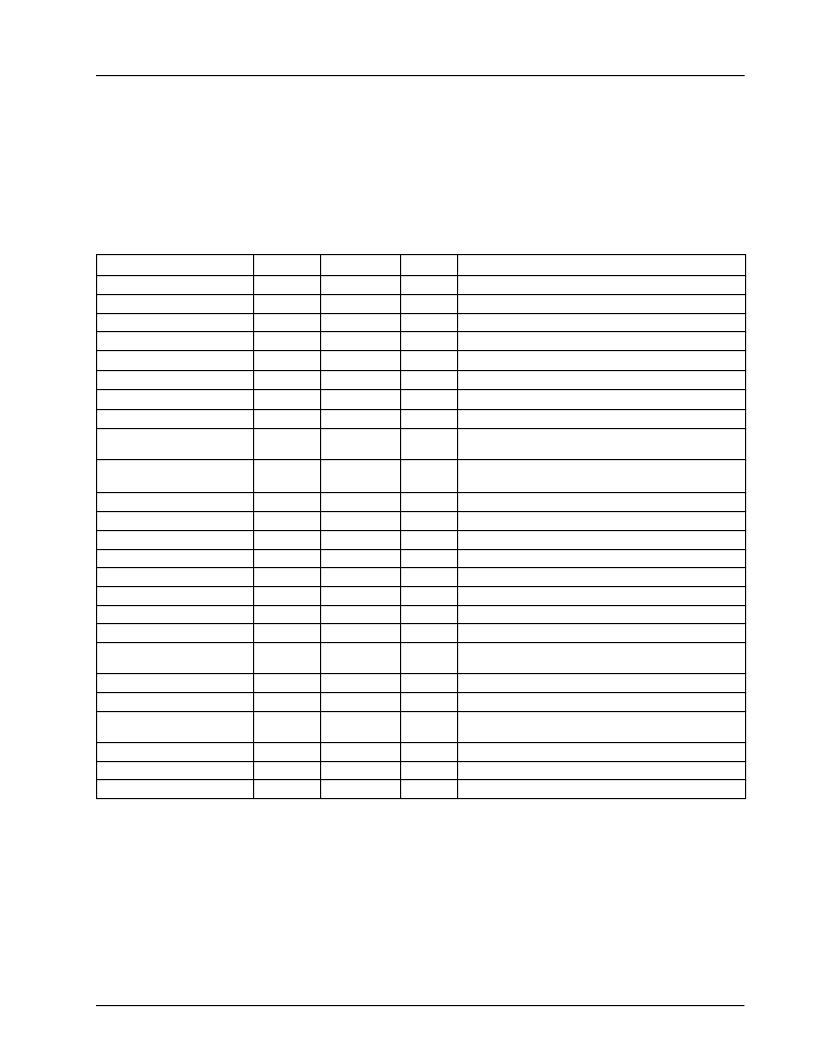

Registers and Programming

The CH7013A is a fully programmable device, providing for full functional control through a set of registers

accessed from the serial port. The CH7013A contains a total of 37 registers, which are listed in

Table15

and

described in detail under

Register Descriptions

. Detailed descriptions of operating modes and their effects are con-

tained in the previous section,

Functional Description.

An addition (+) sign in the Bits column below signifies that

the parameter contains more than 8 bits, and the remaining bits are located in another register.

Table 15. Register Map

Register

Symbol

Address

Bits

Functional Summary

Display Mode

DMR

00H

8

Display mode selection

Flicker Filter

Video Bandwidth

FFR

VBW

01H

03H

6

7

Flicker filter mode selection

Luma and chroma filter bandwidth selection

Input Data Format

IDF

04H

7

Data format and bit-width selections

Clock Mode

CM

06H

8

Sets the clock mode to be used

Start Active Video

SAV

07H

8+

Active video delay setting

Position Overflow

PO

08H

3

MSB bits of position values

Black Level

BLR

HPR

09H

0AH

8

8+

Black level adjustment input latch clock edge select

Enables horizontal movement of displayed image on

TV

Horizontal Position

Vertical Position

VPR

0BH

8+

Enables vertical movement of displayed image on

TV

Determines the horizontal and vertical sync polarity

Sync Polarity

Power Management

SPR

0DH

4

PMR

0EH

5

Enables power saving modes

Connection Detect

Contrast Enhancement

CDR

CE

10H

11H

4

3

Detection of TV presence

Contrast enhancement setting

PLL M and N extra bits

MNE

13H

5

Contains the MSB bits for the M and N PLL values

PLL-M Value

PLL-N Value

PLLM

PLLN

14H

15H

8+

8+

Sets the PLL M value - bits (7:0)

Sets the PLL N value - bits (7:0)

Buffered Clock

BCO

17H

6

Determines the clock output at pin 41

Subcarrier Frequency

Adjust

PLL and Memory Control

FSCI

18H -1FH

4 or 8

each

6

Determines the subcarrier frequency

PLLC

20H

Controls for the PLL and memory sections

CIV Control

Calculated Fsc Increment

Value

CIVC

CIV

21H

22H - 24H

5

8 each

Control of CIV value

Readable register containing the calculated

subcarrier increment value

Version ID

Test

VID

TR

25H

26H - 29H

8

30

Device version number

Reserved for test (details not included herein)

Address

AR

3FH

6

Current register being addressed

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CHB1143 | CHB1143 |

| CHF12545CBF | 500 W Power RF Flanged Chip Termination |

| CHF12545CBF500L | 500 W Power RF Flanged Chip Termination |

| CHF12545CBF500R | 500 W Power RF Flanged Chip Termination |

| CHF190104CBF | 800 W Power RF Flanged Chip Termination/Resistor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CH7013B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Digital PC to TV Encoder |

| CH7013B-D | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Digital PC to TV Encoder |

| CH7013B-DF | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Digital PC to TV Encoder |

| CH7013B-DF-TR | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Digital PC to TV Encoder |

| CH7013B-D-TR | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Digital PC to TV Encoder |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。